Abstract

Graphene Nano Scrolls (GNSs) and Zigzag graphene nanoscrolls (ZGNSs) are semi-one-dimensional materials with exceptional electrical and optical properties, making them attractive to be used in nanoelectronics and complementary metal–oxide–semiconductor (CMOS) technology. With in CMOS device technology, time delay is a crucial issue in the design and implementation of CMOS based ZGNSs. Current paper focus is on ZGNSs application in the channel area of metal–oxide–semiconductor field-effect transistors (MOSFETs) in CMOS technology. We studied analytically, the importance of different parameters on time delay reduction, resulting in faster switching and higher frequency in integrated circuits (ICs). The results of this research demonstrates that, the ZGNS-based CMOS proves considerable variations in the current due to the geometrical parameters, such as chirality number, channel length, and nanoscroll length which can be engineered to produce faster ICs.

Similar content being viewed by others

Introduction

The exceptional and unique physical properties like electrical, mechanical, magnetic, optical and etc. in sensing or actuating methods, play an important role in the science and industry1,2,3,4,5 which motivates the researchers to investigate new materials for future technology. Graphene nanoscroll (GNS) has exceptional electrical and optical properties, making it attractive for researchers in nanoelectronics applications6,7,8,9,10,11. Comparing GNSs with carbon nanotubes (CNTs), Boron Nitro silicon (Si 2 BN)12 or Penta grapheme13 shows that the larger diameter of GNSs and more appropriate accessibility into the interlayer positions of grapheme nanosheets are provided for foreign molecules with unsealed edges/top ends which simplifies the electrolyte infiltration and axial electron transfer10,11,14. As shown in Fig. 1, GNS can be made by rolling a graphene sheet to form an open cylindrical structure. GNS with a tubular structure similar to that of the open CNT has various structures like armchair (n, n), zigzag (n, 0), and chiral (n, m)6,15. As the borders of scrolled sheets of GNSs are not connected, they contain an open morphology dissimilar to multi-walled nanotubes16. Two dissident energy contributions are achieved by controlling scroll configuration and increasing the elastic energy by bending the graphene sheets to decrease free energy and interactions in the overlapping areas of the graphene sheet17. Unrolling back of GNSs into their planar morphology is prevented by the π–π interactions and van der Waals between the overlapping layers9.

These exceptional structural specifications result in unique mechanical, electronic, thermal, and anticorrosive properties of GNS and make them appealing candidates for applications in batteries, ion channels, sensors, supercapacitors, and electronic devices18,19. Quick and efficient carbon nanoscroll based device fabrication with gate/temperature dependent transport mechanism has been reported20, however carbon nano scroll based Complementary metal–oxide–semiconductor (CMOS)fabrication still remain as a challenging research and need to be explored.

Complementary metal–oxide–semiconductor, which is the part of integrated circuits (ICs), and one of the most important electrical components with a enormous applications in electronics, especially in digital electronics. Extensive studies have been done on different types of graphene or CNTs in particular graphene nanoscroll and their applications in nanoelectronics, especially nanoscale transistors, sensors, and various devices10,21,22,23,24,25,26,27,28,29,30,31,32,33,34. Because of their geometry stability and engineerable chirality compare to the planar configurations, ZGNSs have been projected on new generations of nanoelectronic devices26,35,36,37. Conversely time delay as a crucial parameter in the design and implementation of CMOS technology need to be analysed. Because it is the major vital parameter in the dynamic operation of CMOS and has an inverse correlation with speed. The reduction of this parameter leads to faster switching and higher frequency in ICs38. In this paper by calculating and analyzing of time delay in CMOS based zigzag GNS (ZGNS) we are trying to investigate the importance of different factors to reduce time delay, resulting in faster switching and higher frequency in integrated circuits. In the following sections the proposed analytical model, the results, and the main findings of the model are presented.

Proposed analytical model

In order to comprehend the current and time delay calculations for the same and different channel lengths of nanotransistors and identify their physical phenomena, the analytical models and results are presented in this section.

Current calculation in nanotransistors

A general relation for current in nanotransistors states that the current directly relates to carrier concentrations (ni), carrier velocity (v), and cross-section of channel area (A)39. Carrier velocity can be calculated by Eq. (1)40:

where \(\mu_{n}\) is the electron (or hole) mobility and Ecrt is the critical field which is the electrical field throughout the channel when the velocity of carriers reaches the saturation velocity. E is the electrical field along the channel and is considered to be half of the Ecrt. In this paper, the mobility and saturation velocity of CNT has been used instead of their amounts in GNS due to the comparable property of GNS and CNT. Therefore mobility and saturation velocity values are considered 105 (cm2/V∙s) and 2 × 107 (cm/s), respectively41 and the mobility as a function of E-field is unspecified. For simplicity, If we assume that the mobility doesn’t change tangible with E-field changes, Ecrt can be written as Eq. (2)41:

Using the relation (1), carrier velocity (v) can be calculated as 7 × 106 (cm/s). In numerical analysis the effects of variations for channel width are neglected and the channel length assumed to be 200 nm. In the definition of the degenerate and non-degenerate regions, the Fermi level, with a distance more than 3KBT from either the valence or conduction band edge within the band gap, exhibits a non-degenerate condition. Conversely, in the degenerate region, the Fermi level is within 3KBT of either the band edge or lies inside a band42. The carrier concentration of ZGNS in the degenerate region is obtained by Eq. (3)43:

where KB is the Boltzmann constant, T is temperature, \(\hbar\) is the Plank constant, γ is the overlap energy of the carbon–carbon bond which is considered 3.0 eV44. The normalized Fermi energy is defined as \(\eta_{F} = \frac{{E_{F} - E_{C} }}{{K_{B} T}}\) and the effective mass is obtained using Eq. (4)43:

where ac-c is the carbon–carbon bond length, L is the nanoscroll length, and n is the chirality number of nanoscroll. Moreover, the conduction energy is calculated as \(E_{C} = \frac{1}{2}\left[ {\gamma + 3\left( \frac{L}{n} \right)^{2} } \right]\)43, and EF is the Fermi energy that can vary by carrier concentration but in this paper, it is considered to be constant and equal to 0.110 eV45 and the carbon bond length is 1.41 Å; Therefore the carrier concentration of ZGNS in the degenerate regions can can be obtained as:

The drain current ID is equal to \({n}_{{i}_{dg}} \cdot q\cdot v\cdot A\) where \({A=W.L}_{ch}\)39. If we assume that the applied E-field is the half of the critical E-field and by using Eqs. (1) and (5), the drain current as a function of L, Lch and n can be calculated as:

The following three-dimensional (3D) figures show the current function versus two other variables with assuming that the third variable is constant. Figure 2 shows the current curve versus L and n for several different channel lengths. As can be seen, the current along the channel increases with increasing the size of the channel length. The current behavior versus Lch and n for different values of nanoscroll length is illustrated in Fig. 3. The curves are parabolic before a special point and after that suddenly become zero. The amount of this special point along the Lch axis is approximately equal to the nanoscrolls length. For example, the current turns to become zero at Lch = 42 nm for L = 60 nm.

When the carbon nanostructure is curved, tension is induced in the carbon atoms located at the edge and central part of the device therefore a barrier46 is shaped which directs to a p–n junction like performance in the structure. Consequently quasi-saturation behavior is expected47,48.

Figure 4 represent the current curve versus L and Lch for different chirality numbers. In this case, the current increases exponentially and then saturates to a special amount. Also, the current value increases with increasing the chirality number (n).

In this research, only semiconductor GNSs are considered and it is notable fact to know that they are ambipolar semiconductors therefore, the relation (5) is valid in both n- and p-channel transistors for the channels with the same lengths and widths. As ZGNSs in nanoscale size dominated by quantum confinement effect in two cartesian directions, consequently, they can operate in quantum limit. So, the one dimensional current density, \(J\) is equal to \(\left({e}^{2}/\pi {\mathrm{\hslash }}\right){V}_{applied}{T}_{(E)}\). Also, it is expected that these devices can operate in the ballistic limit, therefore, the transmission (T) could be assumed to be 1. Additionally, considering spin selectivity in ZGNS, the current can be modified as \(I=\left({e}^{2}/hA\right){V}_{applied}{T}_{(E)}\). Where, e is the electron charge, A is the cross section of ZGNS,\({V}_{applied}\) is the applied voltage and h is the Plank constant. The comparison study between presented model and simulation results as shown in the Fig. 5 indicates good agreement.

Time delay in CMOS

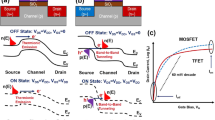

Time delay is an interval time between the “on” and “off” states of a transistor. This parameter is one of the important dynamic properties of CMOS inverters; Decreasing time delay causes faster transistors and consequently CMOS become faster. Figure 6 shows a CMOS that consists two n-channel and p-channel transistors which are connected in series.

CL is a capacitor that is considered in small signal model analysis. VDD is the applied voltage on the source terminal of the p-channel transistor. The Eqs. (7) and (8) represent the time delay for this design49:

where:

\(\tau_{{D_{n} }}\) and \(\tau_{{D_{p} }}\) are the time delay of n-channel and p-channel transistors, respectively50. I is the current along the channel area of transistors. At the following section, the time delay will be studied in two cases of the same and different channel lengths.

Time delay for same channel lengths

By using Eqs. (6), (7), and (8), the time delay for the channel lengths can be obtained as:

As can be seen in the equation, the time delay is a complex function of different parameters such as CL, VDD, L, n, and Lch. CL and VDD values are usually considered as the assumed amounts and time delay is plotted versus the other three variables. The results are plotted in 2D for the following states:

(i) \(\tau_{D}\) versus L: In this case, we have assumed that \(C_{L} = 10fF\) and \(V_{DD} = 1.5V\). Figure 7 shows the time delay of the ZGNS-based CMOS for n = 4 and different channel lengths. In the GNSs with equal chirality number and length, the one with the shortest channel length has the longest time delay. It is noteworthy that the diagrams for lengths of less than 10 nm lost the linear behavior. The observed trend is attributed to the quantum effects.

Figure 8 illustrates the time delay curve for Lch = 20 nm and different chirality numbers. In this case, the quantum effects also appear for lengths of less than 10 nm. Among the GNSs with the same channel length, the one with the largest chirality number has the shortest time delay.

(ii) \(\tau_{D}\) versus n: In this case, the following parameters have been assumed:\(C_{L} = 25fF\) and \(V_{DD} = 2.0V\). Figure 9 indicates the time delay of the CMOS which is plotted for Lch = 20 nm and different nanoscroll lengths. The pick of time delay curves increases significantly with increasing L. Moreover, \(\tau_{D}\) decreases exponentially with increasing n and that is favorable because it makes the CMOS faster. A notable point that can be understood from the diagrams is that for smaller and comparable values of L with channel lengths (L = 10 nm and 30 nm), the diagrams increase up to the pick point then decrease and do not have uniform behavior which isn’t a favorable case. For this reason, it’s suitable that use longer lengths than channel lengths to have a uniform behavior.

Figure 10 is a plot of time delay as a function of n for L = 10 nm and different channel lengths. As can be seen in Fig. 10, the time delay (\(\tau_{D}\)) suddenly becomes zero for \(n \ge 11\). In addition, among the nanoscrolls with equal lengths and chirality numbers, the one with the longest channel length has the shortest time delay.

(iii) \(\tau_{D}\) versus Lch: In this case, we have assumed that \(C_{L} = 15fF\) and \(V_{DD} = 1.8V\). This is a routine case; because the \(\tau_{D}\) behavior versus Lch, is exactly similar to a reciprocal function.

Figure 11 depicts the time delay of the ZGNS-based CMOS for L = 20 nm and different chiralities. Among the nanoscrolls with equal lengths, the one with the biggest chirality number has the shortest time delay.

Figure 12 indicates the time delay curve for n = 3 and different nanoscroll lengths. Apparently, among the nanoscrolls with equal channel lengths, the one with the largest length has the longest time delay.

Time delay for different channel lengths

In current study transistors with different channel lengths are considered, also it is assumed that multiplying of the length and the width of an n-type transistor is equal to that of a p-type transistor, i.e. \({\left({WL}_{ch}\right)}_{n}={\text{m}}{\left({WL}_{ch}\right)}_{p}\), additionally similar carrier concentration and carrier motilities for n-type and p-type transistors \(\left(n=p;{v}_{p}={v}_{n}\right)\) are presupposed; furthermore, based on Eqs. (6), (7) and (8), the time delay for \({C}_{L}=15 fF\) and \({V}_{DD}=1.5 V\) can be obtained as

The Eq. (10) looks like Eq. (9). The difference is just in coefficient term i.e. \(9.1 \times 10^{ - 11}\)\(\left( {\frac{m + 1}{m}} \right)\). Therefore, the time delay for \(m > 1\) has a little difference with a similar case compared to \(0 < m < 1\). For example, the time delay for \(m = 0.1\) is 11 times of a similar case in the same channels. Whereas, for \(m = 3\), the time delay is 1.33 times of similar cases in the same channels. There are three operational possibilities for the decreasing time delay in the ZGNS-based CMOS:

-

1.

The channel length should be increased for constant chirality number and nanoscroll length,

-

2.

The chirality number should be increased for constant channel and nanoscroll length and

-

3.

The nanoscroll length should be decreased for constant chirality number and channel length.

These cases are valid for both CMOS with the same and different transistors as well. Also, using CMOS with the same transistors gives a shorter time delay compared to the different transistors51. In this paper, the temperature effect has been neglected. Modification of some approximations may yield better and more accurate values for the time delay in ZGNS-based CMOS technology.

Simulation study

TCAD simulation based on density functional theory (DFT) method is carried out, in the platform of the metal–semiconductor-metal structure by polarized consideration which gives us spin up and down calculation separately as shown in Fig. 13.

To generate desired ZGNs basic (2, 2) graphene as a GNS building block with several nanometer in length is wrapped 360 degrees (Fig. 14A,B). Generated zigzag GNS is simulated based on DFT method and current–voltage characteristic is presented as shown in Fig. 14C.

Additionally, TCAD simulation for total conductance and thermal conductance is explored. It needs to be notified that the total conductance is higher than the thermal conductance which indicates higher electron transport in comparison with phonon transport as shown in the Fig. 15. In the other words, less energy in the form of heat in these devices are wasted, therefore, low energy consumption is expected compared to the conventional structures.

To explore the morphology effect, Phosphorus (P) and Boron (B) in the zigzag graphene nanoscroll structure is considered and modified devices are characterized as shown in Fig. 16.

It is concluded that ZGNS indicates ambipolar behavior based on the I-V characteristic for P or B doped ZGNS structure which is in line with reported results for carbon based materials such as carbon nano tube and graphene nano ribbon. Variation of current to the bias (dI/dV) that represents the conductance in the Phosphorous doped structure in comparison with the Boron doped structure indicates dramatic disparity almost in all range of the biases. As shown in transmission spectrum (Fig. 17), by applied bias in the channel region transmission is increased in both of the cases. Transmission analysis for different ZGNS shows that Phosphorous generates available transmission states below the Fermi level but Boron generates available states right above the Fermi level.

To investigate the size effect on GNS device performance, different radii are considered as shown in Fig. 18.

As Fig. 18c shows, for negative energy region the transmission profiles are about same but at the positive region one can clearly see that the transmission increased by radius which can be explained by existence of more rooms for electrons in bigger structure.

Conclusion

The application of GNS in complementary metal-oxide-semiconductors (CMOS) is a promising avenue for the advancement of nanoelectronics. This study focuses on calculating and analyzing the time delay in CMOS devices that are based on ZGNS. Time delay is a crucial issue of CMOS dynamic operation and has an inverse relationship with speed. A decrease in this parameter results in faster switching and higher operating frequencies in integrated circuits (ICs). ZGNS-based CMOS shows considerable variations in the current due to parameters such as chirality number, channel length, and nanoscroll length which can be engineered to produce faster ICs. The results of this research show for n = 3 and different nanoscroll lengths, apparently, among the nanoscrolls with equal channel lengths, the one with the largest length has the longest time delay while, for n = 4 and different channel lengths, in the GNSs with equal chirality number and length, the one with the shortest channel length has the longest time delay. On the other hand for Lch = 20 nm and different nanoscroll lengths, among the nanoscrolls with equal lengths and chirality numbers, the one with the longest channel length has the shortest time delay. Also for Lch = 20 nm and different chirality numbers, among the GNSs with the same channel length, the one with the largest chirality number has the shortest time delay. So it can be concluded that the ZGNS-based CMOS can be engineered to increase the current via parameters such as chirality number, channel length, and nanoscroll length to get faster ICs. Finally, this study was a step ahead to shed more light on ZGNS-based CMOS devices and the chirality (zigzag, armchair and chiral), defects, stress, tension and substrate influences need to be considered in the future works.

Data availability

The datasets used and/or analysed during the current study available from the corresponding author on reasonable request.

References

Darbasi, S., Abazari, A. M. & Rezazadeh, G. Mechanical analysis of a tunable capacitive ultrasound transducer using higher order gradient theory. Appl. Math. Model. https://doi.org/10.1016/j.apm.2021.09.031 (2022).

Hassanvand, A., Abazari, A. M., Moradi, R. & Shafee, A. Thermal effects of the nonuniform magnetic force on nanofluid stream along the convergent tube: A computational study. Int. J. Mod. Phys. B https://doi.org/10.1142/S0217979220502641 (2020).

Abazari, A. M., Fotouhi, M., Tavakkoli, H. & Rezazadeh, G. An experimental study for characterization of size-dependence in microstructures via electrostatic pull-in instability technique. Appl. Phys. Lett. https://doi.org/10.1063/5.0011335 (2020).

Darbasi, S., Mirzaei, M. J., Abazari, A. M. & Rezazadeh, G. Adaptive under-actuated control for capacitive micro-machined ultrasonic transducer based on an accurate nonlinear modeling. Nonlinear Dyn. https://doi.org/10.1007/s11071-022-07330-9 (2022).

Mirzaei, A. O. et al. Mutual inductance calculations of non-identical n-sided planar coils with arbitrary geometry and spatial orientations. Eur. Phys. J. Plus https://doi.org/10.1140/epjp/s13360-023-04493-1 (2023).

Rahmani, M., Ghafoori Fard, H., Ahmadi, M. T. & Rahmani, K. Analytical prediction of carbon nanoscroll-based electrochemical glucose biosensor performance. Int. J. Environ. Anal. Chem. https://doi.org/10.1080/03067319.2017.1377521 (2017).

Zheng, B., Xu, Z. & Gao, C. Mass production of graphene nanoscrolls and their application in high rate performance supercapacitors. Nanoscale https://doi.org/10.1039/C5NR07067H (2016).

Dhar, P., Gaur, S. S., Kumar, A. & Katiyar, V. Cellulose nanocrystal templated graphene nanoscrolls for high performance supercapacitors and hydrogen storage: An experimental and molecular simulation study. Sci. Rep. https://doi.org/10.1038/s41598-018-22123-0 (2018).

Ajala, O., Werther, C., Nikaeen, P., Singh, R. P. & Depan, D. Influence of graphene nanoscrolls on the crystallization behavior and nano-mechanical properties of polylactic acid. Polym. Adv. Technol. https://doi.org/10.1002/pat.4615 (2019).

Zhao, Y., Wang, J., Ma, C., Cao, L. & Shao, Z. A self-adhesive graphene nanoscroll/nanosheet paper with confined Fe1−xS/Fe3O4 hetero-nanoparticles for high-performance anode material of flexible Li-ion batteries. Chem. Eng. J. https://doi.org/10.1016/j.cej.2019.03.246 (2019).

Jiang, S. et al. Robust and durable flexible micro-supercapacitors enabled by graphene nanoscrolls. Chem. Eng. J. https://doi.org/10.1016/j.cej.2020.127009 (2021).

Ahani, P., Ahmadi, M. T., Abazari, A. M. & Rahmani, M. Investigation of boron nitro silicone band modulation using the tight-binding method. ECS J. Solid State Sci. Technol. https://doi.org/10.1149/2162-8777/ac95c9 (2022).

Ahmadi, M. T., GozaliBalkanloo, R., Rahmani, M. & Abazari, A. M. Investigation of bond energy effect on the electronic band structure of penta-graphene using tight-binding method. ECS J. Solid State Sci. Technol. https://doi.org/10.1149/2162-8777/ac9255 (2022).

Mohanapriya, K. & Jha, N. Fabrication of one dimensional graphene nanoscrolls for high performance supercapacitor application. Appl. Surf. Sci. https://doi.org/10.1016/j.apsusc.2017.12.186 (2018).

Bejagam, K. K., Singh, S. & Deshmukh, S. A. Nanoparticle activated and directed assembly of graphene into a nanoscroll. Carbon https://doi.org/10.1016/j.carbon.2018.03.077 (2018).

Perim, E., Machado, L. D. & Galvao, D. S. A brief review on syntheses, structures, and applications of nanoscrolls. Front. Mater. https://doi.org/10.3389/fmats.2014.00031 (2014).

Tang, B., Yun, X., Xiong, Z. & Wang, X. Formation of graphene oxide nanoscrolls in organic solvents: Toward scalable device fabrication. ACS Appl. Nano Mater. https://doi.org/10.1021/acsanm.7b00160 (2018).

Huang, X. et al. Graphene-based materials: Synthesis, characterization, properties, and applications. Small https://doi.org/10.1002/smll.201002009 (2011).

Pop, E., Varshney, V. & Roy, A. K. Thermal properties of graphene: Fundamentals and applications. MRS Bull. https://doi.org/10.1557/mrs.2012.203 (2012).

Xie, X. et al. Controlled fabrication of high-quality carbon nanoscrolls from monolayer graphene. Nano Lett. 9, 7. https://doi.org/10.1021/nl900677y (2009).

Khademhosseini, V., Dideban, D. & Ahmadi, M. T. The current analysis of a single electron transistor based on double graphene nanoscroll island. Solid State Commun. https://doi.org/10.1016/j.ssc.2021.114234 (2021).

Ahmadi, M. T., Bodaghzadeh, M., Rahimian Koloor, S. S. & Petrů, M. Graphene nanoparticle-based, nitrate ion sensor characteristics. Nanomaterials https://doi.org/10.3390/nano11010150 (2021).

Khaledian, M., Ismail, R., Saeidmanesh, M., Ghadiry, M. & Akbari, E. Sensitivity modelling of graphene nanoscroll-based NO2 gas sensors. Plasmonics https://doi.org/10.1007/s11468-015-9905-6 (2015).

Yang, B., Zhao, J., Chen, J., He, M. & Xu, S. Controllable synthesis of graphene nanoscroll-wrapped Fe3O4 nanoparticles and their lithium-ion battery performance. RSC Adv. https://doi.org/10.1039/C5RA08855K (2015).

Khademhosseini, V., Dideban, D., Ahmadi, M. T. & Heidari, H. Schemes for single electron transistor based on double quantum dot islands utilizing a graphene nanoscroll, carbon nanotube and fullerene. Molecules https://doi.org/10.3390/molecules27010301 (2022).

Ahmadi, M. T., Ahmadi, R. & Nguyen, T. K. Graphene nanoscroll geometry effect on transistor performance. J. Electron. Mater. https://doi.org/10.1007/s11664-019-07801-7 (2020).

Karimi, H. et al. Analytical prediction of liquid-gated graphene nanoscroll biosensor performance. RSC Adv. https://doi.org/10.1039/C3RA47432A (2014).

Guo, Y. et al. Interwoven V2O5 nanowire/graphene nanoscroll hybrid assembled as efficient polysulfide-trapping-conversion interlayer for long-life lithium–sulfur batteries. J. Mater. Chem. A https://doi.org/10.1039/C8TA06610H (2018).

Khaledian, M., Ismail, R., Saeidmanesh, M. & Khaledian, P. Analytical modeling of the sensing parameters for graphene nanoscroll-based gas sensors. RSC Adv. https://doi.org/10.1039/C5RA01150G (2015).

Guo, Y. et al. Efficient synthesis of graphene nanoscrolls for fabricating sulfur-loaded cathode and flexible hybrid interlayer toward high-performance Li–S batteries. ACS Appl. Mater. Interfaces https://doi.org/10.1021/acsami.6b13455 (2016).

Rahmani, M. et al. Analytical investigation on the electrooptical properties of graphene nanoscrolls for SPR-based sensor application. J. Comput. Electron. https://doi.org/10.1007/s10825-017-1018-3 (2017).

Zhang, Z. et al. Exploration of fast ion diffusion kinetics in graphene nanoscrolls encapsulated CoSe2 as advanced anode for high-rate sodium-ion batteries. Carbon https://doi.org/10.1016/j.carbon.2021.04.095 (2021).

Guo, Y., Zhang, Y., Sun, Y., Zhang, Y. & Wu, H. Graphene-nanoscroll-based Integrated and self-standing electrode with a sandwich structure for lithium sulfur batteries. Inorg. Chem. Front. https://doi.org/10.1039/C9QI01344J (2020).

Islam, M., Rahman, M. M., Chowdhury, M. M. & Alam, M. K. Graphene nanoscrolls via electric-field-induced transformation of water-submerged graphene nanoribbons for energy storage, nanofluidic, and nanoelectronic applications. ACS Appl. Nano Mater. https://doi.org/10.1021/acsanm.9b01304 (2019).

Perim, E. & Galvao, D. S. The structure and dynamics of boron nitride nanoscrolls. Nanotechnology 20, 33. https://doi.org/10.1088/0957-4484/20/33/335702 (2009).

Khaledian, M., Ismail, R. & Akbari, E. Band structures of graphene nanoscrolls and their dispersion relation near the Fermi point. RSC Adv. 6, 45. https://doi.org/10.1039/C5RA27789B (2016).

Chen, Y., Lu, J. & Gao, Z. Structural and electronic study of nanoscrolls rolled up by a single graphene sheet. J. Phys. Chem. C 111, 4. https://doi.org/10.1021/jp066030r (2007).

Baker, R. J. CMOS: Circuit Design, Layout, and Simulation (Wiley, 2019).

Lundstrom, M. S. & Fossum, J. G. Nanoscale Transistors, Device Physics, Modeling and Simulation (Springer, 2006). https://doi.org/10.1093/oso/9780198759874.003.0002.

Ismail, R., Ahmadi, M. T. & Anwar, S. Advanced Nanoelectronics (Taylor & Francis Group, 2013). https://doi.org/10.1201/9781315217185.

Chen, Y. F. & Fuhrer, M. S. Electric-field-dependent charge-carrier velocity in semiconducting carbon nanotubes. Phys. Rev. Lett. https://doi.org/10.1103/PhysRevLett.95.236803 (2005).

Makarovski, A., Liu, J. & Finkelstein, G. Evolution of transport regimes in carbon nanotube quantum dots. Phys. Rev. Lett. https://doi.org/10.1103/PhysRevLett.99.066801 (2007).

Khaledian, M., Ismail, R., Saeidmanesh, M., Ahmadi, M. T. & Akbari, E. Carrier statistics and quantum capacitance models of graphene nanoscroll. J. Nanomater. https://doi.org/10.1155/2014/762143 (2014).

Khaledian, M., Ahmadi, M. T., Ismail, R. & Saeidmanesh, M. Structural and properties of graphene nanobelts rolled up into spiral by a single graphene sheet. J. Comput. Theor. Nanosci. https://doi.org/10.1166/jctn.2014.3401 (2014).

Kim, S. et al. Direct measurement of the Fermi energy in graphene using a double-layer heterostructure. Phys. Rev. Lett. https://doi.org/10.1103/PhysRevLett.108.116404 (2012).

Ding, J. W. et al. Curvature and strain effects on electronic properties of single-wall carbon nanotubes. J. Phys. Condens. Matter. https://doi.org/10.1088/0953-8984/15/27/101 (2003).

Wang, R., Bai, W., Qiao, M., Li, Z., Wang, Z. & Zhang, B. An ultra-low gate charge shield gate MOSFET with pinch-off region and Schottky contact. In 2020 IEEE 15th International Conference on Solid-State and Integrated Circuit Technology (ICSICT), Kunming, pp. 1–3. doi:https://doi.org/10.1109/ICSICT49897.2020.9278384 (2020).

Sharma, C. H. & Thalakulam, M. Split-gated point-contact for electrostatic confinement of transport in MoS2/h-BN hybrid structures. Sci. Rep. 7, 735. https://doi.org/10.1038/s41598-017-00857-7 (2017).

Samanta, J., De, B. P., Bag, B. & Maity, R. K. Comparative study for delay & power dissipation of CMOS Inverter in UDSM range. Int. J. Soft Comput. Eng. (IJSCE) 1(6), 6 (2012).

Ferdous, F., Bhuyan, M. H. & Khosru, Q. D. Carrier diffusion time delay of pocket implanted nano scale n-MOSFET. In 7th International Conference on Electrical and Computer Engineering. IEEE, p. 682. https://doi.org/10.1109/ICECE.2012.6471642 (2012).

Hasanuzzaman, M., Islam, S. K., Tolbert, L. M. & Alam, M. T. Temperature dependency of MOSFET device characteristics in 4H-and 6H-silicon carbide (SiC). Solid-State Electron. https://doi.org/10.1016/j.sse.2004.05.029 (2004).

Funding

The present study was performed as a part of the research in the Nanotechnology Research Center, Nanoelectronics Group, Physics Department, Urmia University, Urmia, Iran.

Author information

Authors and Affiliations

Contributions

Mohammad Taghi Ahmadi and Amir Musa Abazari supervised the team activity. All authors contributed to the study's conception and design. Material preparation, data collection, and analysis were performed by Ali Sadeqian and Morteza Bodaghzadeh. The first draft of the manuscript was written by Ali Sadeqian and Amir Musa Abazari and all authors commented on previous versions of the manuscript. All authors read and approved the final manuscript.

Corresponding authors

Ethics declarations

Competing interests

The authors declare no competing interests.

Additional information

Publisher's note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons licence, and indicate if changes were made. The images or other third party material in this article are included in the article's Creative Commons licence, unless indicated otherwise in a credit line to the material. If material is not included in the article's Creative Commons licence and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this licence, visit http://creativecommons.org/licenses/by/4.0/.

About this article

Cite this article

Sadeqian, A., Ahmadi, M.T., Bodaghzadeh, M. et al. Calculating and analyzing time delay in zigzag graphene nanoscrolls based complementary metal-oxide-semiconductors. Sci Rep 14, 9009 (2024). https://doi.org/10.1038/s41598-024-58593-8

Received:

Accepted:

Published:

DOI: https://doi.org/10.1038/s41598-024-58593-8

Keywords

Comments

By submitting a comment you agree to abide by our Terms and Community Guidelines. If you find something abusive or that does not comply with our terms or guidelines please flag it as inappropriate.