Abstract

With development of information age, multi-valued logic (MVL) technology utilizing negative differential transconductance (NDT) phenomenon has drawn attention as next-generation computing technology that can replace binary logic. However, because conventional NDT devices primarily use ternary logic, multiple-peak NDT device is required for higher-radix MVL that can process more datasets. Here, van der Waals double-peak anti-ambipolar transistor (AAT) as NDT device was developed by utilizing peak voltage (Vpeak) modulation of NDT peak. For realization of quaternary logic, Vpeak modulation technology was developed through charge transfer mechanism from channel, thereby shifting NDT peak and increasing peak-to-valley current ratio (PVCR). Furthermore, Double-peak AAT was implemented through parallel configuration of two AATs with different Vpeak values. Finally, quaternary inverter with four widely stable logic states was implemented by utilizing the developed double-peak AAT with two distinct NDT peaks and high PVCR. This double-peak AAT is expected to contribute to the development of next-generation MVL technology capable of processing datasets.

Similar content being viewed by others

Introduction

With the emergence of the big-data era, multi-valued logic (MVL) technology has attracted attention for next-generation computing systems because it makes higher information density possible by replacing conventional binary logic with ternary or higher-radix logic1,2,3,4,5,6,7,8. The low complexity of the MVL circuit is made possible by the reduction of the interconnect line and cost with increasing the radix of the MVL system1,3,4,9. Conversion from binary logic to ternary and quaternary logic can reduce the circuit complexity by 63.1% and 50%, respectively7,9. Therefore, it is necessary to develop higher-radix MVL circuits capable of processing multiple datasets.

The realization of the MVL circuits has been widely studied by utilizing devices based on negative differential transconductance (NDT)6,10,11,12,13,14 and negative differential resistance (NDR)15,16,17,18. The NDT device has a “Λ-shaped” electrical curve, called the “NDT peak,” in a specific voltage range in the electrical characteristics (ID–VG)19,20. When the NDT device is integrated with a transistor for the MVL circuit, the number of NDT peaks determines the number of additional intermediate logic states in the MVL compared with binary logic5,21,22,23. Therefore, to develop higher-radix MVL, it is necessary to increase the number of NDT peaks in NDT devices.

The anti-ambipolar transistor (AAT) has been widely utilized as an NDT device to realize MVL circuits3,11,13. The AAT has a distinct NDT peak and a simple device structure composed of n- and p-type heterostructures24,25,26. The main parameters of NDT peak are the peak voltage (Vpeak) and the peak-to-valley current ratio (PVCR). These two parameters of the NDT peak determine the stable operation of the MVL circuit. The Vpeak is defined as the overlapping point between n- and p-type electrical curves27,28. In addition, in AAT, a high PVCR of the NDT peak can be formed by a large overlapping area between the high on/off switching characteristics of the two semiconductors27,28,29,30,31. Owing to the high PVCR of the NDT peak, the AAT can induce a widely stable intermediate logic state of the MVL circuit by forming a widely matched electrical curve region between the AAT and integrated transistor11,32,33,34,35. Therefore, the AAT can realize an MVL circuit with low complexity, high reliability, high-speed logic data processing, and a low process level.

Because the AAT is composed of a pn junction, it is necessary to form a high-quality heterointerface to prevent deterioration of the electrical performance11,13,21,22,32,34,35,36. The van der Waals (vdW) heterostructure based on two-dimensional (2D) materials, such as MoS2, WSe2, WS2, etc., has been employed recently in the development of AATs for the realization of MVL circuits owing to the formation of high-quality heterointerfaces with low interfacial defects owing to the absence of a dangling bond37,38,39,40,41,42,43,44. Therefore, the vdW heterostructure-based AAT with a high PVCR and simple device structure can be used to realize an MVL circuit with high reliability, high-speed logic data processing, and a low process level.

Double-peak NDT devices are beginning to be developed for the implementation of quaternary logic as a next step in MVL technology to overcome the challenges of ternary logic3,5,12,45. However, conventional double-peak NDT devices have a high process level and structure with at least four materials because the formation of two NDT peaks requires many n/p-type electrical curves5. In addition, conventional double-peak NDT devices have a low PVCR because of the low overlapping region between the n/p-type electrical curves45. Therefore, to overcome the disadvantages of conventional double-peak NDT devices, it is necessary to develop a concept of double-peak NDT devices with low process level and excellent NDT characteristics.

In this study, a double-peak AAT was developed using Vpeak modulation technology, which can control the NDT peak of an AAT. This Vpeak modulation technology was achieved by shifting the electrical curves through the charge transfer of WSe2 channel in an AAT based on a MoS2/WSe2 heterostructure. The mechanism of the Vpeak modulation technology was demonstrated by electrical and structural analyses. Furthermore, to realize quaternary logic, a double-peak AAT with a high PVCR and a large difference between two Vpeak values was implemented by connecting two AATs with different Vpeak values in parallel. Finally, a quaternary logic inverter was realized experimentally by utilizing the developed double-peak AAT.

Results and discussion

Device structure and characteristics

Figure 1a shows a schematic diagram of a AAT w/AuCl3 based on a MoS2/WSe2 heterostructure. MoS2 and WSe2 were chosen as the heterostructure materials in the AAT owing to their heterostructure with a type-II band alignment11,13,46. The AuCl3 layer on the WSe2 channel was covered in the AAT based on the MoS2/WSe2 heterostructure. The AuCl3 layer acts as a p-type dopant that can increase the hole concentration in the WSe2 channel. For the fabrication of this AAT w/AuCl3, the MoS2 and WSe2 flakes were stacked on a SiO2 90 nm substrate using a polydimethylsiloxane (PDMS) stamp. The Ti and Pt contact metals were used for the MoS2 and WSe2 channels, respectively. Detailed information related to the contact metal is presented in Supplementary Fig. 1. As shown in Figure 1a, the AAT w/ AuCl3 consisted of MoS2 and WSe2 field-effect transistors (FETs). Then, by transferring h-bn on MoS2, it was used as a cover protection layer—more details are shown in Supplementary Fig. 2. Next, the AuCl3 dopant layer on the WSe2 channel of the AAT was deposited using a spin-coating method. The detailed information of AuCl3 concentration optimization process is presented in Supplementary Fig. 3. The presence of AuCl3 dopant on WSe2 was confirmed using X-ray diffraction (XRD)—more details are shown in Supplementary Fig. 4. Figure 1b shows a top-view optical image of the AAT w/ AuCl3.

a 3D schematic diagram of AAT w/ AuCl3. b Optical image of AAT w/ AuCl3. c AFM height profiles of MoS2 and WSe2, respectively, in heterostructure. d Raman spectra of three regions for MoS2, WSe2, and MoS2/WSe2. e XPS spectra of Au4f obtained from WSe2 and WSe2 w/ AuCl3. Electrical curves (IDS–VBG) of f MoS2 channel, g WSe2 channel w/ AuCl3, and h AAT w/ AuCl3, at VDS = 2 V.

Various structural properties of the AAT w/ AuCl3 were measured. Figure 1c shows the height profiles of WSe2 and MoS2 in the heterostructure of the AAT measured using atomic force microscopy (AFM). The thicknesses of MoS2 and WSe2 were 30 and 43 nm, respectively. The detailed information related to the thickness of channel is presented in Supplementary Fig. 5. Figure 1d shows the Raman spectra of the WSe2, MoS2, and MoS2/WSe2 heterojunctions. The Raman peaks of WSe2 were observed at 249.4 and 257.9 cm−1, corresponding to the E12g + A1g (E + A) and the 2LA vibration modes, respectively. The MoS2 region exhibited vibrational peaks at 384.3 and 409.5 cm−1, corresponding to E12g and A1g, respectively. The Raman spectra of the overlapped MoS2/WSe2 heterojunction show combined peaks of WSe2 (E + A, 2LA) and MoS2 (E12g, A1g)47,48. The X-ray photoelectron spectroscopy (XPS) measurements were performed on the WSe2 w/o and w/ AuCl3, respectively, to confirm the presence of AuCl3 dopants on the WSe2 channel, as shown in Fig. 1e. The XPS spectra of Au 4 f on WSe2 confirmed the AuCl3 peaks, which appeared at Au3+ (91.0 eV), Au04f5/2 (87.40 eV), and Au04f7/2 (84.4 eV)49.

To investigate the detailed electrical characteristics of the AAT w/ AuCl3, Fig. 1f, g shows the electrical curves (IDS–VBG) of MoS2 and WSe2 w/ AuCl3, respectively, at VDS = 2 V. The electrical curves of the two channels were measured using two electrodes in each channel, as shown in Fig. 1a. Figure 1g shows the electrical curve of the WSe2 channel, which is an p-doped area by the AuCl3 dopant. Figure 1h shows the electrical curves of AAT w/ AuCl3. The source and drain of the AAT used end electrodes of MoS2 and WSe2, respectively, as shown in Fig. 1a. A NDT peak formed in the overlapping region between the electrical curves of MoS2 and WSe2 w/ AuCl3. As shown in Fig. 1h, the main parameters of the NDT peak are Vpeak and the PVCR, composed of Ipeak/Ivalley.

The charge transfer mechansim analysis for V peak modulation technology

Figure 2 shows the doping effect demonstration of AuCl3 on WSe2 channel for Vpeak modulation of NDT peak, including the mechanism schematic, electrical and various doping effect analysis. Figure 2a presents the cross-sectional schematic of AAT w/ AuCl3. For channel doping, the WSe2 surface was deposited with AuCl3, as presented in Fig. 2a (red dotted box), because the AuCl3 possess Au3+ ions act as electron acceptors, the p-doping effect can be induced by the charge transfer process of electrons on the WSe2 channel surface to AuCl350,51,52. From these p-doping effect of AuCl3 through charge transfer, as shown in Fig. 2b, it was confirmed that the work function of WSe2 channel was increased due to the hole accumulation by p-doping effect of AuCl3 dopants. Thus, the work function value of WSe2 was increased by 0.13 eV from 4.85 eV to 4.98 eV, by AuCl3 doping effect as presented in Fig. 2b and Supplementary Fig. 6 (numerical analysis). This KPFM analysis results have indicated that the WSe2 channel can be accumulated for high hole concentration, by increasing the work function of WSe2, owing to the p-doping effect. Figure 2c shows the electrical curves of the WSe2 channel in the AAT w/o and w/ AuCl3, respectively, at VDS = 2 V. As shown in Fig. 2c, after p-doping in the WSe2 channel, VTH shifted in the positive direction. Simultaneously, Ion increased after p-doping53,54,55. Figure 2d shows a quantitative numerical analysis of the WSe2 electrical characteristics, including Ion and VTH. When the AuCl3 dopant covered the WSe2 channel, VTH increased from 30 to 35 V. Then, Ion increased by a factor of 59.8 from 1.67 × 10−7 to 9.97 × 10−6 A.

a 2D cross-sectional AAT device and AuCl3 p-doping process on WSe2 schematic illustration for the Vpeak modulation. b The work function of WSe2 w/o and w/ AuCl3, respectively. c Electrical curve of WSe2 channel before and after p-doping, respectively. d Quantitative analysis for VTH and Ion of WSe2 channels w/o and w/ AuCl3. e The Raman spectra, and f the Raman peak shifted quantitative values, including the E12g + A1g, 2LA of the WSe2 w/o and w/ AuCl3. The XPS spectra of g W4f, and h Se3d obtained from the WSe2 w/o and w/ AuCl3.

To demonstrate the p-doping effect of AuCl3 on WSe2, Fig. 2e, f present the Raman and XPS spectra of w/o and w/ AuCl3, respectively.

Figure 2e shows the Raman spectra of WSe2 w/o and w/ AuCl3, respectively. As shown in Fig. 2e (black solid line), two vibrational Raman peaks (E + A and 2LA) were observed near the 250 cm−1 and 259 cm−1 in WSe2 w/o AuCl3. At 250 cm−1, this Raman peak is the combination peak of the in-plane (E12g) and the out-of-plane (A1g) vibration mode. After p-doping of WSe2 w/ AuCl3, as shown in Fig. 2e (red solid line), two Raman peaks (E + A and 2LA) were red-shifted from conventional peaks of WSe2 w/o AuCl3. The red-shifted values of two peaks, which are E + A and 2LA, were 1.1 cm−1 and 0.6 cm−1, respectively, and the quantitative analysis was presented in Fig. 2f. To investigate the precise analysis of the p-doping effect, the XPS analysis were performed in WSe2 w/o and w/ AuCl3, respectively. Figure 2g, h shows the XPS spectra of W4f and Se3d, respectively, which include the WSe2 w/o and w/ AuCl3, respectively. As shown in Fig. 2g, the binding energy for the W4f5/2, W4f7/2 peaks was down-shifted by 0.25 eV. The two peaks for Se3d3/2, Se3d5/2 were down-shifted by 0.625 eV and 0.25 eV, respectively, as shown in Fig. 2h.

Compared to previous studies related p-doping analysis, our Raman and XPS analysis results have matched the shifted direction of XPS peak by the AuCl3 p-type dopant. Therefore, from this result, as the AuCl3 dopant was deposited on WSe2, it was clearly demonstrated that the WSe2 channel is affected by p-doping.

Additionally, to support the demonstration of p-doping effect of AuCl3, analysis of WSe2 using photoluminescence (PL) spectroscopy was presented in Supplementary Fig. 7.

Electrical demonstration of V peak modulation technology

Figure 3 shows the electrical demonstration of the Vpeak modulation technology of NDT peak, including the electrical characteristics, and quantitative analysis. The Vpeak modulation technology can shift the NDT peak through the p-doping effect of WSe2 channel in AAT. Because the Vpeak is defined as the overlapping point between the electrical curves of n-type MoS2 and p-type WSe2, the Vpeak can be modulated by controlling the electrical curve of n- or p-type channel. More detailed information of Vpeak modulation mechanism is presented in Supplementary Fig. 8.

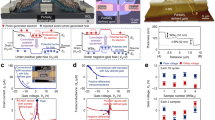

Electrical curves of AATs a w/o and b w/ AuCl3, including the MoS2 and WSe2 channels. c Electrical curves of NDT peak of AATs w/o and w/ AuCl3 at linear scale. d Vpeak value (left y-axis) and PVCR (right y-axis, log scale), corresponding to the AATs w/o and w/ AuCl3. e Box plot of Vpeak, including 14 samples obtained from the AATs w/o and w/ AuCl3 (median values (m) of 12 V and 25 V, standard deviation (σ) of 3.32 V and 2.68 V, standard error (SE) of 0.8 V and 0.7 V, respectively). f Box plot of PVCR, including 13 samples obtained from the AATs w/o and w/ AuCl3 (m of 296 and 1.3 ×104, σ of 144 and 1.5 ×104, SE of 4.3 and 4.5 ×103, respectively).

Figure 3a, b shows the electrical curves, including the AAT, before and after p-doping of the WSe2, respectively. These electrical curves include the MoS2 and WSe2 channels of the AAT. The measured 2D cross-sectional AAT schematic diagrams are presented in Supplementary Fig. 9, before and after p-doping. As shown in Fig. 3a, in the AAT w/o AuCl3, at VDS = 2 V, the NDT peak, which is a Λ-shaped electrical curve, formed in the specific gate voltage region where the electrical curves between the two types of semiconductor overlapped. Subsequently, the p-doping process was performed by covering the AuCl3 layer on the WSe2 channel of the AAT. Figure 3b shows the electrical curve of the AAT w/ AuCl3, at VDS = 2 V. Compared with the AAT w/o AuCl3, because the electrical curve of WSe2 was shifted by p-doping, the NDT peak simultaneously changed, as shown in Fig. 3b. Additionally, while the WSe2 channel of AAT is affected by the p-doping effect of AuCl3, the MoS2 channel with the h-bn protection layer is hardly affected by doping —more details are presented in Supplementary Fig. 10. The electrical characteristics of AAT w/ AuCl3 in Fig. 3b were consistently maintained at various VDS. This detailed information of electrical curves of AAT w/ AuCl3 at various VDS are presented in Supplementary Fig. 11. For a detailed analysis of the NDT peak, Fig. 3c shows the NDT electrical curves of the AATs w/o and w/ AuCl3 at linear scale. The NDT peak of the AAT w/ AuCl3 clearly shifted in the positive direction compared with the AAT w/o AuCl3. In addition, after p-doping of the WSe2 channel, the PVCR of the AAT w/ AuCl3 increased owing to dramatically transition of Ipeak compared with AAT w/o AuCl3. More information of NDT electrical curves at log scale are presented in Supplementary Fig. 12. To investigate the quantitative analysis, Fig. 3d presents the values of the NDT peak parameters (Vpeak and PVCR) in the AATs w/o and w/ AuCl3. As shown in Fig. 3d, the value of Vpeak increased from 15 to 25 V because of the p-doping effect. Similarly, the PVCR increased by approximately 100 times from 102 to 104 for the WSe2 channel before and after p-doping of AuCl3. In particular, the enhancement of PVCR through this Vpeak modulation technology can lead to the formation of highly reliable wide logic state in the MVL circuit. To confirm the reliability of the Vpeak modulation technology, Fig. 3e shows the device-to-device variation of Vpeak for AAT 14 samples before and after p-doping, respectively. As shown in Fig. 3e, after p-doping, the Vpeak of the AAT increased overall. Additionally, Fig. 3f presents the device-to-device variation of PVCR for AAT 13 samples before and after p-doping, respectively. From this result, after p-doping, the PVCR of AAT increased about ~100 times. Therefore, for the AAT, Vpeak modulation technology through WSe2 w/ AuCl3 is highly reliable.

Double-peak AAT implementation using V peak modulation technology

Figure 4 shows a demonstration of the double-peak AAT using two AATs with different Vpeak values. Figure 4a shows a three-dimensional (3D) schematic illustration of the double-peak AAT. The two AATs, which are w/o and w/ AuCl3 with different Vpeak values, were connected in a parallel configuration. In the parallel configuration, three terminals—the source, drain, and gate—were simultaneously connected. Figure 4b shows the equivalent circuit strategy for implementing the double-peak AAT. When the two AATs w/o and w/ AuCl3 were connected in parallel, to realize two clear NDT peaks of the double-peak AAT, the two AATs, each with a difference of more than 20 V in Vpeak, were used. Through the connection of the two AATs, it was possible to realize a double-peak AAT with a high PVCR and two clearly distinguishable NDT peaks. As shown in Fig. 4b, the drain currents of the AATs w/o and w/ AuCl3 are I1 and I2, respectively. Because of the parallel configuration, the drain current of the double-peak AAT is the total current (Itotal = I1 + I2), which adds to the drain currents of the two AATs, as shown in Fig. 4b.

a 3D schematic illustration of double-peak AAT. b Circuit configuration of double-peak AAT. c Electrical characteristics of double-peak AAT, including AATs w/o and w/ AuCl3, at VDS = 2 V. d Electrical characteristics of double-peak AAT, at VDS = 1, 1.5, 2 V. e Vpeak and f PVCR values, Peaks 1 and 2, of double-peak AAT, at VDS = 1, 1.5, 2 V.

Figure 4c shows the electrical curve of the double-peak AAT at VDS = 2 V, which includes the electrical curves of the AATs w/o and w/ AuCl3. Peaks 1 and 2 of the double-peak AAT were observed at two Vpeak values. More detailed information of log and linear scale based electrical curves are presented in Supplementary Figure 13. Additionally, for verification of double NDT phenomenon, more detailed information of transconductance (gm) is presented in Supplementary Figure 14. Figure 4d shows the electrical curve of double-peak AAT with various VDS. As shown in Fig. 4d, as VDS increased, it was confirmed that two distinct NDT peaks of double-peak AAT were observed despite of the transition of the electrical curve. Figure 4e shows a quantitative analysis of the two peaks (Peak 1, Peak 2) in the double-peak AAT with various VDS. At VDS = 2 V, NDT peaks appeared at 3 and 27 V. This confirmed that Peaks 1 and 2 clearly appeared because the highest difference in Vpeak was high (24 V). In addition, Fig. 4f shows the PVCRs of Peak 1, Peak 2 at various VDS. As shown in Fig. 4f, at VDS = 2 V, as the highest PVCR values, the PVCRs of Peaks 1 and 2 were approximately 1063 and 46, respectively. From these results, this confirmed the highest PVCR and a large difference between the two Vpeak values compared with the performance of conventional double-peak NDT/NDR devices5,15,17,18,45,56. Therefore, a double-peak AAT with a high PVCR and distinct NDT peaks was developed by utilizing AATs and Vpeak modulation technology.

Quaternary Inverter Using Double-Peak AAT

Figure 5 shows quaternary inverter applications. Figure 5a shows a 3D schematic illustration of the quaternary inverter circuit, integrating the double-peak AAT. To operate the quaternary inverter, a double-peak AAT was connected to the p-FET. The supply voltage (VDD) and ground (VSS) were applied to the drain metal electrode of the p-FET and the source metal electrode of the double-peak AAT, respectively. The input voltage (Vin) was applied to the back gate electrodes of the double-peak AAT and p-FET. Then, the output voltage (Vout) was connected to the metal electrode between the VDD of the p-FET and the ground of the double-peak AAT. For a clear understanding of the 3D schematic circuit, Fig. 5b shows the circuit configuration of the quaternary inverter. When the double-peak NDT device with two NDT peaks is integrated into the MVL circuit, owing to the formation of two matched electrical curve regions between the double-peak NDT device and integrated transistors, the double-peak NDT device can implement a quaternary inverter with four logic states, in contrast to a binary inverter with two logic states. Figure 5c shows the voltage transfer characteristics (VTCs) of the quaternary inverter circuit. At VDD = 2 V, four stable regions formed as logic states when Vin from 50 to −10 V was applied. The four logic states appeared at Vout = 2 V for −10 V < Vin < 10 V (State 3), Vout = 1.5 V for 15 V < Vin < 26 V (State 2), Vout = 1 V for 30 V < Vin < 37 V (State 1), and Vout = 0 V for 41 V < Vin < 50 V (State 0). More information of working mechanism of quaternary inverter is presented in Supplementary Figure 15.

Because the developed double-peak AAT has two NDT peaks, two intermediate logic states (States 2 and 1) can be formed by increasing the number of overlapping regions between the double-peak AAT and the p-FET5,6,11,21,22,23. Separately, owing to the on-state of the p-FET in a negatively high Vin region from −10 to 10 V, a low-resistance path can be formed between the VDD and the output terminal. The Vout was measured as a VDD of 2 V, and this high logic state is State 3. Then, Vout was measured as 0 V in the high-Vin region owing to the off-state of the p-FET, and this low-logic state is State 0. The detailed information related to inverter operation with number of NDT peak is presented in Supplementary Fig. 16.

Finally, Fig. 5d shows the dynamic output characteristics of the quaternary inverter circuit with the application of random Vin waveforms. When −10 V, 15 V, 30 V, and 50 V, which may generate the 4-logic states in the VTC of Fig. 5c, are applied to the input terminal, the quaternary inverter circuits produce 3, 2, 1, 0 logic states as Vout, as shown in Fig. 5d. These results means that the developed double-peak AAT can be evolved to quaternary logic gate applications such as NAND, NOR, AND, OR, etc.

The research indicators for the double-peak NDT/NDR device are provided in Table 15,15,17,18,45,56. This double-peak AAT has a high PVCR of 103, with a large difference between the two Vpeak values of 24 V compared with the performance of conventional double-peak NDT/NDR devices. A high-performance quaternary inverter with a relatively low VDD of 2 V and wide logic state of 20 V was experimentally implemented using the high-performance double-peak AAT. Therefore, the high-performance characteristics of the developed double-peak AAT show that the developed device can have a significant impact on next-generation MVL technology, surpassing conventional ternary logic.

Discussion

A double-peak AAT based on a vdW heterostructure was developed as a candidate for the implementation of quaternary logic by utilizing the Vpeak modulation technology of the NDT peak in an AAT. By shifting the electrical curves through the AuCl3 p-doping of WSe2 channel in the control AAT based on the MoS2/WSe2 heterostructure, the Vpeak of the NDT peak was drastically shifted by 10 V from 15 to 25 V, resulting in the AAT w/ AuCl3. In addition, the PVCR of the AAT w/o AuCl3 increased by approximately 100 times from 102 to 104 when the Ion of the WSe2 channel was increased because of the p-doping effect. Furthermore, the double-peak AAT was demonstrated experimentally by connecting the AATs w/o and w/ AuCl3 in parallel. This double-peak AAT had a PVCR of ~103 and a Vpeak difference of 24 V between the two NDT peaks. Finally, a quaternary inverter with four widely stable logic states of 20 V was implemented using the developed double-peak AAT. Therefore, the developed double-peak AAT is promising for the development of an MVL system to overcome the limitations of conventional ternary logic.

Methods

AuCl3 solution preparation

The AuCl3 and toluene solutions were purchased from Sigma-Aldrich. In this study, 0.02 g of AuCl3 was added to 45 mL of a toluene buffer solution for a concentration of 1.5 mM. The AuCl3 solution was sonicated for more than 1 h and mixed evenly.

Device fabrication

The SiO2 (90 nm)/p-Si substrate was cleaned using a sonicator in acetone, isopropyl alcohol, and deionized water. The MoS2/WSe2 heterostructure was fabricated using a PDMS transfer technique. The MoS2 and WSe2 flakes were mechanically exfoliated using Nitto tape. MoS2, as the bottom layer, was transferred onto the SiO2 substrate using a PDMS stamp. Next, WSe2 was stacked on MoS2 using the vdW pick-up transfer method and a PDMS/glass plate. The source/drain (S/D) of the heterostructure was patterned using photolithography. Ti/Au (70/10 nm) and Pt/Ti/Au (20/50/10 nm) were deposited onto the S/D regions of the MoS2 and WSe2, respectively, using an e-beam evaporator. Subsequently, lift-off was performed to form the S/D region of the device based on the heterostructure. Next, to open the WSe2 channel in the heterostructure, the MoS2 channel was covered with h-bn using a polypropylene carbonate/PDMS transfer method. To control the NDT properties of the AAT, the WSe2 channel was covered with AuCl3 dopant using a spin coater at 5500 rpm for 35 s. After the AuCl3 dopant was coated on the WSe2 channel, the AAT was baked at 105 °C for 1 min.

Structure and electrical characteristics measurements

AFM was performed to confirm the thicknesses of the MoS2 and WSe2 flakes. Raman spectroscopy was used to analyze the heterostructure and doping technique. The XRD measurements were performed to confirm the presence of AuCl3 (Supplementary Information). XPS, PL spectroscopy, and KPFM were used to analyze the doping technique. To determine the electrical characteristics of the NDT peak devices, the electrical transfer curve (IDS–VBG), which was swept backward from 50 to −50 V, was measured using a Keithley-4200 instrument. Finally, the VTCs (Vout–Vin and Vout–time) diagrams of the quaternary inverter were measured using the Keithley-4200.

Data availability

The authors declare that the supporting data are available in Supplementary information on the npj 2D materials & applications website.

References

Sandhie, Z. T., Patel, J. A., Ahmed, F. U. & Chowdhury, M. H. Investigation of Multiple-valued Logic Technologies for Beyond-binary Era. ACM Comput Surv. 54, 1–30 (2021).

Park, S. et al. Quaternary NAND Logic and Complementary Ternary Inverter with p-MoTe2/n-MoS2 Heterostack Channel Transistors. Adv. Funct. Mater. 32, 2108737 (2022).

Andreev, M., Seo, S., Jung, K. S. & Park, J. H. Looking Beyond 0 and 1: Principles and Technology of Multi-Valued Logic Devices. Adv. Mater. 34, 2108830 (2022).

Jo, S. B., Kang, J. & Cho, J. H. Recent Advances on Multivalued Logic Gates: A Materials Perspective. Adv. Sci. 8, 2004216 (2021).

Lim, J. H. et al. Double Negative Differential Transconductance Characteristic: From Device to Circuit Application toward Quaternary Inverter. Adv. Funct. Mater. 29, 1905540 (2019).

Shim, J. et al. Light-Triggered Ternary Device and Inverter Based on Heterojunction of van der Waals Materials. ACS Nano 11, 6319–6327 (2017).

Yoo, H. & Kim, C. H. Multi-valued logic system: New opportunities from emerging materials and devices. J. Mater. Chem. C. 9, 4092–4104 (2021).

Doostaregan, A., Moaiyeri, M. H., Navi, K. & Hashemipour, O. On the design of new low-power CMOS standard ternary logic gates. In Proceedings - 15th CSI International Symposium on Computer Architecture and Digital Systems, CADS 2010 115–120 (IEEE, 2010).

Hurst, S. L. Multiple-Valued Logic—Its Status and Its Future. IEEE Trans. Comput. C–33, 1160–1179 (1984).

Xiong, X. et al. Reconfigurable Logic-in-Memory and Multilingual Artificial Synapses Based on 2D Heterostructures. Adv. Funct. Mater. 30, 1909645 (2020).

Nourbakhsh, A., Zubair, A., Dresselhaus, M. S. & Palacios, T. Transport properties of a MoS2/WSe2 heterojunction transistor and its potential for application. Nano Lett. 16, 1359–1366 (2016).

Seo, S. et al. Controllable potential barrier for multiple negative-differential-transconductance and its application to multi-valued logic computing. NPJ 2D Mater. Appl 5, 32 (2021).

Li, Y. et al. Anti-Ambipolar Field-Effect Transistors Based on Few-Layer 2D Transition Metal Dichalcogenides. ACS Appl Mater. Interfaces 8, 15574–15581 (2016).

Andreev, M. et al. Negative differential transconductance device with a stepped gate dielectric for multi-valued logic circuits. Nanoscale Horiz. 5, 1378–1385 (2020).

Jung, K. S. et al. Double Negative Differential Resistance Device Based on Hafnium Disulfide/Pentacene Hybrid Structure. Adv. Sci. 7, 2000991 (2020).

Shim, J. et al. Phosphorene/rhenium disulfide heterojunction-based negative differential resistance device for multi-valued logic. Nat. Commun. 7, 13413 (2016).

Seo, S. et al. A Van Der Waals Reconfigurable Multi-Valued Logic Device and Circuit Based on Tunable Negative-Differential-Resistance Phenomenon. Adv. Mater. 34, 2202799 (2022).

Kim, K. H. et al. A multiple negative differential resistance heterojunction device and its circuit application to ternary static random access memory. Nanoscale Horiz. 5, 654–662 (2020).

Lee, S., Lee, Y. & Kim, C. Extraordinary transport characteristics and multivalue logic functions in a silicon-based negative-differential transconductance device. Sci. Rep. 7, 11065 (2017).

Xiong, X. et al. A transverse tunnelling field-effect transistor made from a van der Waals heterostructure. Nat. Electron 3, 106–112 (2020).

Duong, N. T. et al. Modulating the Functions of MoS2/MoTe2 van der Waals Heterostructure via Thickness Variation. ACS Nano 13, 4478–4485 (2019).

Huang, M. et al. Multifunctional high-performance van der Waals heterostructures. Nat. Nanotechnol. 12, 1148–1154 (2017).

Kobashi, K., Hayakawa, R., Chikyow, T. & Wakayama, Y. Multi-Valued Logic Circuits Based on Organic Anti-ambipolar Transistors. Nano Lett. 18, 4355–4359 (2018).

Shingaya, Y. et al. Dual-Gate Anti-Ambipolar Transistor with Van der Waals ReS2/WSe2 Heterojunction for Reconfigurable Logic Operations. Adv. Electron Mater. 9, 2200704 (2023).

Wakayama, Y. & Hayakawa, R. Antiambipolar Transistor: A Newcomer for Future Flexible Electronics. Adv. Funct. Mater. 30, 1903724 (2020).

Cheng, R. et al. Anti-Ambipolar Transport with Large Electrical Modulation in 2D Heterostructured Devices. Adv. Mater. 31, 1901144 (2019).

Kobashi, K., Hayakawa, R., Chikyow, T. & Wakayama, Y. Device Geometry Engineering for Controlling Organic Antiambipolar Transistor Properties. J. Phys. Chem. C. 122, 6943–6946 (2018).

Kobashi, K., Hayakawa, R., Chikyow, T. & Wakayama, Y. Interface Engineering for Controlling Device Properties of Organic Antiambipolar Transistors. ACS Appl Mater. Interfaces 10, 2762–2767 (2018).

Panigrahi, D., Hayakawa, R., Fuchii, K., Yamada, Y. & Wakayama, Y. Optically Controlled Ternary Logic Circuits Based on Organic Antiambipolar Transistors. Adv. Electron Mater. 7, 2000940 (2021).

Panigrahi, D., Hayakawa, R. & Wakayama, Y. Antiambipolar Transistor with Double Negative Differential Transconductances for Organic Quaternary Logic Circuits. Adv. Funct. Mater. 33, 2213899 (2023).

Yoo, H. & Kim, C. H. Unified Compact Model for Thin-Film Heterojunction Anti-Ambipolar Transistors. IEEE Electron Device Lett. 42, 1323–1326 (2021).

Lee, Y. et al. Demonstration of Anti-ambipolar Switch and Its Applications for Extremely Low Power Ternary Logic Circuits. ACS Nano 16, 10994–11003 (2022).

Hayakawa, R., Honma, K., Nakaharai, S., Kanai, K. & Wakayama, Y. Electrically Reconfigurable Organic Logic Gates: A Promising Perspective on a Dual-Gate Antiambipolar Transistor. Adv. Mater. 34, 2109491 (2022).

Kobashi, K., Hayakawa, R., Chikyow, T. & Wakayama, Y. Negative Differential Resistance Transistor with Organic p-n Heterojunction. Adv. Electron Mater. 3, 1700106 (2017).

Kim, C. H., Hayakawa, R. & Wakayama, Y. Fundamentals of Organic Anti-Ambipolar Ternary Inverters. Adv. Electron Mater. 6, 1901200 (2020).

Wakayama, Y., Kim, C. H., Panigrahi, D. & Hayakawa, R. Recent progress in organic antiambipolar transistor development: fundamentals and applications. Mater. Adv. 3, 5260–5273 (2022).

Kim, J. Y. et al. Distinctive Field-Effect Transistors and Ternary Inverters Using Cross-Type WSe2/MoS2Heterojunctions Treated with Polymer Acid. ACS Appl Mater. Interfaces 12, 36530–36539 (2020).

Novoselov, K. S., Mishchenko, A., Carvalho, A. & Castro Neto, A. H. 2D materials and van der Waals heterostructures. Science 353, aac9439 (2016).

Yang, R. et al. Heterointerface effects of lithium intercalation and diffusion in van der Waals heterostructures. Phys. Rev. Mater. 6, 094011 (2022).

Teng, Y. et al. Engineering multinary heterointerfaces in two-dimensional cobalt molybdenum phosphide hybrid nanosheets for efficient electrocatalytic water splitting. Sustain Energy Fuels 5, 3458–3466 (2021).

Yao, H., Wu, E. & Liu, J. Frequency doubler based on a single MoTe2/MoS2 anti-ambipolar heterostructure. Appl Phys. Lett. 117, 123103 (2020).

Yan, R. et al. Esaki Diodes in van der Waals Heterojunctions with Broken-Gap Energy Band Alignment. Nano Lett. 15, 5791–5798 (2015).

Nakamura, K. et al. All 2D Heterostructure Tunnel Field-Effect Transistors: Impact of Band Alignment and Heterointerface Quality. ACS Appl Mater. Interfaces 12, 51598–51606 (2020).

Hu, R., Wu, E., Xie, Y. & Liu, J. Multifunctional anti-ambipolar p-n junction based on MoTe2/MoS2 heterostructure. Appl Phys. Lett. 115, 073104 (2019).

Son, H. et al. Complementary driving between 2D heterostructures and surface functionalization for surpassing binary logic devices. ACS Appl Mater. Interfaces 13, 8692–8699 (2021).

Roy, T. et al. Dual-gated MoS2/WSe2 van der Waals tunnel diodes and transistors. ACS Nano 9, 2071–2079 (2015).

Yang, M. et al. Anharmonicity of monolayer MoS2, MoSe2, and WSe2: A Raman study under high pressure and elevated temperature. Appl Phys. Lett. 110, 093108 (2017).

Fan, S., Yun, S. J., Yu, W. J. & Lee, Y. H. Tailoring Quantum Tunneling in a Vanadium-Doped WSe2/SnSe2 Heterostructure. Adv. Sci. 7, 1902751 (2020).

Lee, I. H. et al. Hygroscopic effects on AuCl3-doped carbon nanotubes. J. Phys. Chem. C. 114, 11618–11622 (2010).

Park, K. H. et al. Electron donor or acceptor behavior of a AuCl3 dopant manipulated by dip-pen nanolithography on a MoS2 thin-film transistor. Appl Surf. Sci. 588, 152846 (2022).

Liu, X. et al. P-Type Polar Transition of Chemically Doped Multilayer MoS2 Transistor. Adv. Mater. 28, 2345–2351 (2016).

Liu, X. et al. Homogeneous molybdenum disulfide tunnel diode formed via chemical doping. Appl Phys. Lett. 112, 183103 (2018).

Zhang, R., Drysdale, D., Koutsos, V. & Cheung, R. Controlled Layer Thinning and p-Type Doping of WSe2 by Vapor XeF2. Adv. Funct. Mater. 27, 1702455 (2017).

Han, K. H. et al. Reduction of Threshold Voltage Hysteresis of MoS2 Transistors with 3-Aminopropyltriethoxysilane Passivation and Its Application for Improved Synaptic Behavior. ACS Appl Mater. Interfaces 11, 20949–20955 (2019).

Kang, D. H. et al. High-Performance Transition Metal Dichalcogenide Photodetectors Enhanced by Self-Assembled Monolayer Doping. Adv. Funct. Mater. 25, 4219–4227 (2015).

Paul Inbaraj, C. R. et al. A Bi-Anti-Ambipolar Field Effect Transistor. ACS Nano 15, 8686–8693 (2021).

Acknowledgements

This research was supported by the Basic Science Research Program within the Ministry of Science, ICT, and Future Planning through the National Research Foundation of Korea under Grant 2020R1A2C2004029 and was supported in part by the National Research Foundation of Korea (NRF) funded by the Ministry of science, ICT & Future Planning (RS-2023-00257003).

Author information

Authors and Affiliations

Contributions

K.H. H. and H.-Y. Y. conceived and designed the experiments. K.H. H., S.-H. K., S.-G. K., and J.-H. K. contributed to the experimental process review and device fabrication. K.H. H. fully manufactured the device and performed the electrical characteristics measurement. S.-H. K., S.-G. K., J.-H. K. and S.S. analyzed the data. H.-Y. Y. supervised the research. All the authors discussed the results and commented on the manuscript.

Corresponding author

Ethics declarations

Competing interests

The authors declare no competing interests.

Additional information

Publisher’s note Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Supplementary information

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons licence, and indicate if changes were made. The images or other third party material in this article are included in the article’s Creative Commons licence, unless indicated otherwise in a credit line to the material. If material is not included in the article’s Creative Commons licence and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this licence, visit http://creativecommons.org/licenses/by/4.0/.

About this article

Cite this article

Han, K.H., Kim, SH., Kim, SG. et al. Charge transfer mechanism for realization of double negative differential transconductance. npj 2D Mater Appl 8, 15 (2024). https://doi.org/10.1038/s41699-024-00454-z

Received:

Accepted:

Published:

DOI: https://doi.org/10.1038/s41699-024-00454-z