Abstract

Graphene is a promising material for applications as a channel in graphene field-effect transistors (GFETs) which may be used as a building block for optoelectronics, high-frequency devices and sensors. However, these devices require gate insulators which ideally should form atomically flat interfaces with graphene and at the same time contain small densities of traps to maintain high device stability. Previously used amorphous oxides, such as SiO2 and Al2O3, however, typically suffer from oxide dangling bonds at the interface, high surface roughness and numerous border oxide traps. In order to address these challenges, here we use 2 nm thick epitaxial CaF2 as a gate insulator in GFETs. By analyzing device-to-device variability for about 200 devices fabricated in two batches, we find that tens of them show similar gate transfer characteristics. Our statistical analysis of the hysteresis up to 175oC has revealed that while an ambient-sensitive counterclockwise hysteresis can be present in some devices, the dominant mechanism is thermally activated charge trapping by border defects in CaF2 which results in the conventional clockwise hysteresis. We demonstrate that both the hysteresis and bias-temperature instabilities in our GFETs with CaF2 are comparable to similar devices with SiO2 and Al2O3. In particular, we achieve a small hysteresis below 0.01 V for equivalent oxide thickness (EOT) of about 1 nm at the electric fields up to 15 MV cm−1 and sweep times in the kilosecond range. Thus, our results demonstrate that crystalline CaF2 is a promising insulator for highly-stable GFETs.

Similar content being viewed by others

Introduction

Graphene is a promising material with numerous fascinating properties1,2 which can be attractive for applications in optoelectronics3, sensing4 and radio-frequency electronics5. Like any other field-effect device, graphene field-effect transistors (GFETs)3,4,6 require high-quality insulators to separate the gate from the channel. However, conventionally used amorphous oxides such as SiO2, Al2O3 and HfO2 form ill-defined interfaces with 2D materials which degrade the mobility and contain numerous border traps7 which cause severe hysteresis8,9 and long-term drifts of the gate transfer characteristics10. As of now, the only alternative gate insulator which has been used in GFETs is hBN which enables high mobility11,12,13. However, synthesis of high-quality hBN films on large-area substrates typically requires temperatures of more than 800oC14 which does not match the thermal budget of complementary metal-oxide-semiconductor (CMOS) technologies. As a result, despite the progress already achieved in the technologies of graphene devices, the lack of suitable insulators is a central obstacle for the production of commercially competitive GFETs which will complicate their use, for instance, in currently discussed CMOS-X circuits in which 2D elements could become an X-factor which will enhance scaling capabilities of Si CMOS15.

As a promising alternative to amorphous oxides and hBN, here we use 2 nm thick epitaxial calcium fluoride (fluorite, CaF2) as a gate insulator in scalable GFETs with a graphene channel grown by chemical vapor deposition (CVD) and transferred onto the CaF2 substrate. CaF2 is an ionic crystalline insulator with good dielectric properties (Eg = 12.1 eV, ε in range between 6.816 and 8.4317) which forms quasi van der Waals interfaces with 2D materials18 and at the same time can be epitaxially grown on Si(111) at 250oC19 in line with CMOS thermal budget requirements. This, in particular, makes CaF2 an attractive candidate for the gate insulator of 2D FETs, even more so as CaF2 allows the heteroepitaxy of 2D semiconductors on CaF2(111), as already confirmed for MoSe220 and MoTe221. In our recent works22,23 we have used CaF2 to fabricate MoS2 FETs with equivalent oxide thicknesses (EOT) down to 1 nm and with promising performance characteristics, such as a subthreshold swing (SS) down to 90 mV dec−1, on/off current ratios up to 107 and high stability with respect to hysteresis and long-term drifts of the gate transfer characteristics. Recently it has been also shown that CaF2 can be epitaxially grown on silicene24 which opens the path towards future top gate integration of 2D materials.

Thus, as the next step in this work we extend our previous findings towards More than Moore electronics based on 2D materials which suffers from similar problems of forming high quality interfaces with insulators with few charge traps10. We open a way to the further development of scalable GFETs with various fluoride materials not limited to CaF2 but including also MgF2 or SrF225,26,27 and attempt to estimate the real potential of CaF2/graphene technologies by benchmarking the device-to-device variability, hysteresis and bias-temperature instabilities (BTI) of the gate transfer characteristics. We examine about 200 GFETs with different channel dimensions and study the hysteresis and BTI dynamics in these devices for a broad range of temperatures from 25oC to 175oC. After minimizing the impact of non-insulator defects by annealing at 175oC, we demonstrate that the stable clockwise hysteresis as well as the BTI drifts in our GFETs with CaF2 are comparable to those in GFETs and MoS2 FETs with SiO2 and Al2O3, despite being subjected to higher gate bias stresses. It is worth noting that the use of thin insulators allows to achieve gate fields of up to 15 MV cm−1 which is higher than in most previously studied devices with 2D channels and goes in line with our previous study showing excellent dielectric stability of thin CaF2 layers28. This constitutes the worst case scenario in terms of gate bias stress and thus makes the small observed degradation more valuable. Therefore, we conclude that CaF2 is a promising insulator for next-generation graphene technologies, including Hall sensors for high temperature applications29 which would benefit from stable behavior of our GFETs at least up to 175oC. Furthermore, by using just 2 nm thick CaF2 layers we achieve CMOS-compatible gate voltage operation ranges of only several Volts for our GFETs, while also reducing the power consumption and improving the sensitivity.

Although our first proof-of-concept GFETs with CaF2 do not yet offer outstanding performance in terms of mobility, we demonstrate excellent device stability and reliability owing to the crystalline CaF2 grown at only 250 oC. These results should boost future research on direct CVD growth of graphene on CaF2 and adaptation of more mature dry transfer methods of 2D films30 to achieve the formation of high quality quasi-van der Waals interfaces with CaF2(111) while avoiding the ubiquitous polymer contamination from the transfer process31.

Results

CaF2/graphene devices

Our devices are single-layer back-gated GFETs fabricated by conventional photolithography on Si/CaF2 substrates. Thin layers of CaF2 (2 nm, EOT ~ 1 nm) were grown on moderately doped (ND = 1015 cm−3) and highly doped (ND = 5 × 1018 cm−3) n-Si(111) substrates (Batch#1 and Batch#2, respectively) using an established molecular beam epitaxy method at a growth temperature of 250oC19, similar to our previous works on CaF2/MoS2 FETs22,23. To avoid leakage currents from the large contact pads, they have been isolated with 10 nm Al2O3 layers grown by plasma enhanced atomic layer deposition before sputtering 25 nm Pd source and drain contacts. Next, a commercial CVD-grown graphene film was transferred onto the substrate using a PMMA assisted transfer method and patterned with an oxygen plasma. We note that our metal contact process for graphene was optimized in a way to avoid the formation of corner structures such as lift-off edges near the source and drain electrodes. Their absence has been verified by using atomic-force microscopy (AFM), see Supplementary Fig. 1. More details about the CaF2 growth and fabrication process of our GFETs can be found in the Methods section.

The schematic layout of our GFETs is shown in Fig. 1a. The obtained arrays contain hundreds of devices with channel dimensions (L × W) from 160 μm × 100 μm down to 9 μm × 3 μm, the optical images of the device structures with different dimensions are shown in Fig. 1b–d. In Fig. 1e we show that the gate leakage current is negligible as compared to the drain current while also being far below the density of 1 A cm−2 at VG = 1 V, a guideline for scaled devices32. As demonstrated in Fig. 1f, typical ID-VG characteristics of our devices with L × W = 80 μm × 50 μm exhibit relatively high currents up to 32 μA μm−1 within few Volts operation range due to the highly downscaled thickness of the gate insulator to only 2 nm. At the same time, the ID-VD characteristics presented in Fig. 1g show good current control with some kinks typical for ambipolar GFETs33. Using a similar fabrication process but without isolating the contact pads, we also fabricated similar back-gated GFETs on highly doped Si substrates with 90 nm SiO2 and 36 nm Al2O3 and used them as a reference when comparing the obtained results.

a Schematic structure of our back-gated GFETs with 2 nm CaF2 insulators. Optical images of GFETs with L × W of 160 μm × 100 μm (b), 80 μm × 50 μm (c) and smaller dimensions from 40 μm × 20 μm to 9 μm × 3 μm (d). e The gate leakage current through our thin CaF2 layers is small compared to the drain current through the GFET channel with a density far below 1 A cm−2 at VG = 1 V. f Typical ID-VG characteristics of our GFETs measured at different drain voltages. g The ID-VD characteristics measured for the same GFET at different gate voltages exhibit ambipolar kinks. All provided results have been obtained for Batch#1 GFETs.

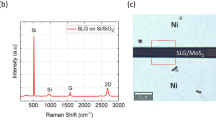

We also note that since this is the first proof of concept study of GFETs with CaF2 which employs transferred graphene films and non-protected channels, we did not focus on achieving the highest possible field-effect mobilities. Thus, the typical mobility measured using four-probe measurements ranges between 700 and 1000 cm2V−1s−1 which is low compared to most previous studies for GFETs with SiO211 and hBN11,12,13. However, it is expected that a more carefully adjusted device fabrication process could result in considerably improved mobilities owing to the quasi van der Waals nature of the CaF2/graphene interface. In particular, the results of our Raman spectrum measurements for graphene transferred onto CaF2 suggest that some strain may be introduced to the film (see Supplementary Fig. 2 for more details). This is likely due to the chemical inertness of CaF2(111) surfaces18 and thus has to be avoided, for instance by developing specific transfer methods for this type of substrates. Furthermore, long ambient exposure of the CaF2 surface prior to fabrication of GFETs was unavoidable for these prototypes but should be minimized in the future.

Device-to-device variability

We start with a statistical analysis of the ID-VG characteristics measured for our GFETs with different sizes. As shown in Fig. 2a for our Batch#1 GFETs fabricated on moderately doped Si, already at this early stage of research over 30% of devices from the most representative group of GFETs with 80 μm × 50 μm dimensions exhibit very similar or even nearly identical ID-VG characteristics, even though in overall the device-to-device variability is still sizable (see Supplementary Fig. 3). In Fig. 2b we show the distribution of the Dirac current vs. Dirac voltage points (IDirac vs. VDirac) for all 116 studied devices and note that the variability is stronger for GFETs with smaller channels. This is likely because our CVD-grown graphene is polycrystalline with a typical grain size of more than 80 μm as specified by the manufacturer, and thus larger devices may contain several complete grains within the channel, while the channel area of their smaller counterparts can be affected considerably by the grain boundaries. Since these grain boundaries significantly affect the electrostatics and carrier transport in the channel, broader distributions of IDirac and VDirac for smaller devices are to be expected. Furthermore, the same argumentation holds true for local imperfections and charges at the CaF2 surface. In general, it is expected that there are microscopic inhomogeneities in the grown CaF2 layers and impurities that have attached to the CaF2 surface during transport and processing before the graphene layer transfer. These atomic defects will have a more pronounced impact on the charge transport for small area devices as compared to larger area ones34. Another factor contributing to the variability could be different contact resistances of the pads due to some imperfections in their processing (see Supplementary Fig. 4). Thus, we expect that by further optimizing the CVD growth of the graphene channel and the device fabrication techniques, as well as the CaF2 growth and the overall device fabrication flow, it may be possible to considerably reduce this variability.

a ID-VG characteristics of 11 similar GFETs with 80 μm × 50 μm channels selected from our total statistics of 116 Batch#1 devices with different channel dimensions. b Distribution of IDirac vs. VDirac for all 116 devices; the number of devices with the corresponding channel dimension is marked in brackets in the legend. The measurements have been performed before any annealing step and some smaller devices have a more positive VDirac (for those GFETs we used a VG sweep range from 0 to 4 V), implying the existence of a significant amount of negative charge at the interface.

In Supplementary Fig. 5 we also show that GFETs from Batch#2 which we have fabricated later on highly doped Si substrates have very similar ID-VG characteristics and variability trends. Unlike Batch#1 devices, before the measurements they have been subjected to initial annealing consisting of 2 days at 100 oC and 5 h at 175 oC. At the same time, our reference GFETs with 36 nm Al2O3 insulators typically exhibit larger variability in VDirac but lower variations in drain current (Supplementary Fig. 6). This could hint at a higher quality of the graphene films after their transfer onto a non-inert Al2O3 surface but at the same time larger and more variable number of fixed charges at the graphene/Al2O3 interface as compared to graphene/CaF2.

In addition, we have repeated the variability measurements on our Batch#1 GFETs following 6 months of storage under a moderate vacuum of about 600 torr. We found that at least 35 out of 116 GFETs remained functional and thus analyzed the device-to-device variability under the impact of elevated temperatures, while ignoring about 10 % of outliers with too positive VDirac above 2 V (Fig. 2b) in our statistics. As shown in Fig. 3a for one representative GFET, at room temperature the measured ID-VG characteristic does not change significantly following long storage. However, annealing at 175oC results in a negative shift of VDirac which becomes more pronounced after a week at high temperature and does not recover after cooling back to 25 oC. This is likely caused by evaporation of some impurities from graphene or adsorbates which could serve as fixed charges and affect VDirac. The IDirac vs. VDirac distributions obtained for 35 devices with channel dimensions ranging from 40 μm × 20 μm down to 9 μm × 3 μm (Fig. 3b) suggest that this negative drift of VDirac is a common feature for all GFETs on CaF2. This could be attributed to the evaporation of some impurities which causes the initial p-doping of our graphene and also affects the work function of graphene35 and thus the device electrostatics. As a result, the symmetry of the ID-VG characteristics of our GFETs may also change after annealing, as will be clear from the results provided below. At the same time, the variability in VDirac becomes smaller after annealing, as also confirmed by the statistical distributions shown in Fig. 3c. It is also remarkable that the variability measured at the end of our 1 week long annealing round (orange color) is considerably lower than it was during the first 3 hours at 175oC (red color). Thus, we suggest that a thermal treatment of the devices at 175 oC should allow to exclude side effects related to the ambient impact on our GFETs, thus revealing the hysteresis dynamics which could be attributed solely to border insulator defects in CaF2.

a Transformation of the ID-VG characteristics following 6 months of storage under a moderate vacuum, subsequent annealing at 175 oC and cooling back to 25 oC. b Distribution of IDirac vs. VDirac for 35 devices at 25 oC, in the beginning and in the end of 175 oC annealing in vacuum (10−6 torr), and at 25 oC after annealing. c Statistical distributions of VDirac values for these devices at the same temperature/annealing conditions and at VD = 0.3 V.

Hysteresis dynamics and reliability

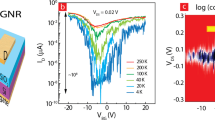

In Fig. 4 we analyze the hysteresis dynamics in GFETs with 80 μm × 50 μm channels. Among five selected devices, four are from Batch#1 which have not experienced any annealing and one is from Batch#2 which has been subjected only to initial annealing, i.e. 2 days at 100 oC followed by 5 h at 175 oC. We can see that all devices have similar ID-VG characteristics which confirms the good reproducibility of our GFET technology. The hysteresis width (ΔVH) vs. reciprocal sweep time (1/tsw) dependencies36 measured for these GFETs are shown in Fig. 4b. While all devices from Batch#1 exhibit switching of the hysteresis from counterclockwise at faster sweeps to clockwise at slower sweeps, a typical GFET from Batch#2 has only a small clockwise hysteresis. In Supplementary Fig. 7 we show the ID-VG characteristics of these devices measured using different sweep rates and observe that the clockwise hysteresis which appears for slow sweeps for Batch#1 GFETs is accompanied with a permanent negative drift of VDirac. We suggest that while the conventional clockwise hysteresis is caused by fast insulator defects located close to the CaF2/graphene interface, the permanent drift accumulated during multiple sweeps is similar to bias-temperature instabilities (BTI) known from Si technologies37, thus being a consequence of the charging of slower insulator defects in CaF2 which have time constants in the range of kiloseconds. Remarkably, for the GFETs from Batch#2 both the hysteresis and negative drift of VDirac are considerably less pronounced, which could mean that the work function of graphene used in our second fabrication round is more favorable to energetically suppress the charge trapping by defects in CaF235.

a Double sweep ID-VG characteristics of five GFETs with 80μm × 50 μm channels measured using ultra-slow sweeps with S = 0.002 V s−1. Among these devices, there is one GFET from Batch#2. b The ΔVH vs. 1/tsw dependencies for the same GFETs. Compared to GFETs from Batch#1, the device from Batch#2 has only a small clockwise hysteresis at slow sweeps with no counterclockwise hysteresis at fast sweeps.

To understand the origins of the observed hysteresis dynamics and in particular the counterclockwise hysteresis, we have performed a similar analysis on GFETs with smaller channel areas before thermal annealing. In Fig. 5a, b we show the ID-VG characteristics of Batch#1 GFETs with 9 μm × 3 μm and 40 μm × 20 μm channel dimensions which exhibit similar hysteresis at different sweep rates. As confirmed in Fig. 5c for a larger statistics of seven GFETs, despite the overall variability in ΔVH(1/tsw) curves, some devices with different sizes show nearly identical hysteresis dynamics. Thus, this variability is not directly related to the channel dimensions but rather to the local density and type of defects near the channel. At the same time, it is remarkable that some of these smaller GFETs exhibit a counterclockwise hysteresis even at slow sweeps, while the others have purely clockwise hysteresis which becomes larger for slow sweeps and thus indicates a standard charge trapping mechanism at border traps in the CaF2 close to the channel. To benchmark the origin of the counterclockwise hysteresis, we have also performed hysteresis measurements after 10 minutes of ambient exposure. As shown in Supplementary Fig. 8, in the device with initially dominant counterclockwise hysteresis this hysteresis becomes more pronounced following the ambient exposure, while the clockwise hysteresis in the second device slightly decreases without any switching to the counterclockwise direction. Therefore, we suggest that this counterclockwise hysteresis is mostly due to the interaction of our bare channel GFETs with the ambient environment while being unlikely related to defects in CaF2. The possible reasons for this behavior could include, for instance, interaction of defects in graphene with adsorbates or the diffusion of oxygen through imperfections in CaF2 to the Si/CaF2 interface. A counterclockwise hysteresis could for example be caused by charge trapping at defects close to the gate side, formed by the Si/CaF2 interface38.

Double sweep ID-VG characteristics of GFETs with 9 μm × 3 μm (a) and 40 μm × 20 μm (b) channels measured with different sweep rates. The hysteresis dynamics observed for these two devices are very similar. c The ΔVH vs. 1/tsw dependencies for seven GFETs with different channel dimensions. While there is some variability in the hysteresis dynamics, some devices with different sizes have identical hysteresis and thus this effect appears to be independent of the channel dimensions.

In this context, we next analyze the impact of high temperature annealing on the hysteresis in our GFETs directly after ambient exposure. In Fig. 6a, b we show the ID-VG characteristics of two GFETs with counterclockwise (Device A) and clockwise (Device B) hysteresis at different temperatures up to 175 oC and back at 25 oC after six days annealing required to complete our measurements at 175 oC. Indeed, the counterclockwise hysteresis in Device A can be considerably suppressed (Fig. 6c), which makes the initially different ΔVH(1/tsw) traces of two GFETs nearly identical after annealing (Fig. 6d). Furthermore, in Batch#2 GFETs (Fig. 6e, f) we do not see any counterclockwise hysteresis and observe only a conventional thermal activation of clockwise hysteresis which is consistent with our previous findings about charge trapping by border insulator defects situated near the interface with 2D channels36,39. Remarkably, after about one week at 175oC the hysteresis in these GFETs remains small and the dynamics observed at 25 oC do not change. This suggests that the density of border defects in CaF2 is relatively low and that there is no thermally induced creation of new defects. Also, we note that the clockwise hysteresis in Batch#2 GFETs is smaller as compared to their Batch#1 counterparts, which could be explained by a more favorable work function35 of the graphene films used during the second fabrication round.

Double sweep ID-VG characteristics measured for our Batch#1 GFETs at T = 25 oC, 175 oC and 25 oC after annealing using S = 0.002 V s−1. Just after 10 min of ambient exposure, Device A (a) exhibited counterclockwise and Device B (b) clockwise hysteresis. c At 100 oC and at 175 oC the counterclockwise hysteresis in Device A is strongly suppressed, and after annealing at 175 oC both devices exhibit similar clockwise hysteresis (d). e, f The corresponding results for a Batch#2 GFET which show no counterclockwise contribution and conventional thermal activation of charge trapping. These GFETs experienced an initial annealing of 2 days at 100 oC and 5 h at 175 oC prior to the first measurement round.

Next we perform bias-temparature instability (BTI) measurements for the Batch#2 GFET studied in Fig. 6e, f using increased gate bias stress VG,stress, constant stress time ts = 10 ks and recovery voltage VG,rec = − 0.4 V. The results obtained after 1 week of annealing at 175 oC are shown in Fig. 7. It is clear that despite extremely high insulator fields up to 15 MV cm−1, both negative BTI (NBTI) (Fig. 7a, VG,stress < 0V) and positive BTI (PBTI) (Fig. 7b, VG,stress > 0V) drifts are comparatively small. At the same time, no anomalous trends are present. This is in line with a small clockwise hysteresis measured for the same device which is actually a superposition of NBTI and PBTI accumulated during the sweeps40 and again confirms low density of border traps in CaF2. At the same time, the recovery of the observed degradation is rather weak in both cases, which suggests contributions from deep trap levels in CaF2. This is in line with our first principle calculations for possible defects in CaF2 which could be Si interstitials (Sii) or Si substituting Ca (SiCa) energetically aligned deep in the bandgap of CaF238.

Discussion

In order to accurately compare the measured hysteresis and BTI shifts of our CaF2 GFETs to the results on FETs with different gate stacks, the measured hysteresis widths ΔVH and Dirac point shifts ΔVDirac are normalized by EOT. As both the hysteresis in the gate transfer charactersitics and BTI are caused by charge trapping, the following relation holds

with the elementary charge q, the density of active charge traps, NT, and the insulator capacitance Cins = ε0εr/dins. Hence, by introducing the equivalent oxide thickness (EOT = \({\varepsilon }_{{{{{\rm{SiO}}}}}_{{{{\rm{2}}}}}}/{\varepsilon }_{{{{\rm{r}}}}}\times {d}_{{{{\rm{ins}}}}}\)) we obtain

with the SiO2 dielectric constant of 3.9. As a consequence, the normalized hysteresis width is directly proportional to the density of active charge traps, NT, with physical constants as proportionality factors. Using this normalization, we compare in Fig. 8a the post-annealing hysteresis observed for our CaF2 GFETs, for back-gated MoS2 FETs with SiO236,41 and CaF222, for commercial silicon FETs and also for our reference back-gated GFETs with SiO2 and Al2O3 (see more details in Supplementary Fig. 9). ΔVH/EOT measured at tsw = 2 ks is plotted versus the effective gate insulator field \(({V}_{{{{\rm{G,max}}}}}-{V}_{{{{\rm{G,min}}}}})\)/dins, where \({V}_{{{{\rm{G,max}}}}}\) and \({V}_{{{{\rm{G,min}}}}}\) are the boundaries of the gate sweep range, and also versus EOT. Indeed, owing to the crystalline CaF2 and the highly scaled insulator thickness, the observed hysteresis is small and comparable to the normalized hysteresis observed in other devices, even at high effective gate insulator fields. This comparison shows that the density of activated charge traps NT in our Batch#2 GFETs is minimal, leading to the best observed performance. Moreover, for the Batch#2 GFETs the targets of ΔVH < 0.01 V for EOT < 1 nm and a gate field of \({{{{\mathcal{E}}}}}_{{{{\rm{ins}}}}}\, > \,10\) MV cm−1 are reached, showing a smaller hysteresis than measurements on a commercial Si/high-k technology. For reference we show a similar comparison in Supplementary Fig. 10 without any normalization, directly comparing the measured ΔVH, demonstrating how a scaled EOT is very important to achieve small absolute numbers for the hysteresis width, ΔVH and further illustrating the excellent performance of our GFETs.

a Comparison of the normalized hysteresis widths in different back-gated 2D FETs (1-36 2-41 3-22) and Si FETs for the sweep time of about 2 ks versus the effective gate field \(({V}_{{{{\rm{G,max}}}}}-{V}_{{{{\rm{G,min}}}}})\)/dins (left) and versus EOT (right). For comparing the hysteresis widths on technologies with different gate stacks, the hysteresis widths were normalized by EOT. The measured clockwise hysteresis in our GFETs with CaF2 is comparable to the normalized hysteresis widths reported in 2D devices, with the hysteresis on our Batch#2 CaF2 GFETs being the smallest and meeting the target values. b Comparison of normalized PBTI (top) and NBTI (bottom) drifts measured with a small time delay of about 0.5 s after stress and after 10 hours of recovery versus the insulator field VG,stress/dins (left) and versus EOT (right). Measured Dirac shifts were normalized by EOT, revealing a comparable BTI on our GFETs with CaF2 as in devices with SiO2 and Al2O3 gate insulators, despite being stressed at much higher gate fields. In both (a) and (b) we use one best device for each technology.

Additionally, in Fig. 8b we compare the NBTI and PBTI shifts of the Dirac voltage normalized by EOT as a function of the stress insulator field and EOT for our GFETs with CaF2, Al2O3 and SiO2 to the BTI on a commercial silicon high-k scaled logic node42. For the three GFET batches, the absolute stress voltages were 3, 10 and 30 V, respectively. In agreement with the hysteresis results for GFETs with CaF2, the normalized BTI shifts are comparable for all three gate insulators, even though CaF2 has experienced considerably higher electric fields. In the CaF2 GFETs the electric gate fields and EOT targets are achieved, even though the BTI target of 0.03 V according to the International Roadmap of Semiconductor Devices and Systems43 is out of reach for any of the compared GFET technologies. Again, in Supplementary Fig. 10a comparison of the directly measured ΔVDirac values is shown, confirming the small BTI seen in our CaF2 gated GFETs. These results demonstrate that CaF2 is a promising insulator which allows to fabricate ultra-scaled 2D devices of high stability with respect to charge trapping.

In summary, we fabricated about two hundred GFETs with CVD-grown graphene channels and 2 nm thick epitaxial CaF2 insulators and performed an in-depth study of the device-to-device variability and hysteresis dynamics. Our results show that although grain boundaries of the channel or imperfections in CaF2 layers may introduce some variability in the gate transfer characteristics, some nearly identical GFETs can be found already at this early stage of research. We have also performed a comprehensive statistical analysis of hysteresis and BTI on many GFETs at temperatures of up to 175 oC. Our findings suggest that the initially observed, ambient-sensitive, counterclockwise hysteresis can be fully suppressed by 175 oC annealing in our first batch of GFETs and is not present in the devices from the second batch. The remaining clockwise hysteresis can be attributed to border traps in CaF2 and is on devices from the second batch smaller than in reference GFETs with SiO2 and Al2O3. The main milestone of our study is that we have achieved a hysteresis below 0.01 V for an equivalent oxide thickness (EOT) of about 1 nm at electric fields up to 15 MV cm−1 and long sweep times in the kilosecond range, reaching the target values set by commercial silicon technologies. These results confirm that the use of crystalline CaF2 as a gate insulator is a promising way to enable stable GFETs for sensors and optoelectronics, including Hall sensors for high temperature operations. Our findings can be generalized to include applications of various 2D materials and their devices for heterogeneous electronics coupling 2D and silicon CMOS elements44.

Methods

Device fabrication

Fabrication of our GFETs consists of MBE growth of 2 nm thick CaF2 films and photolithography to produce the device arrays with channel dimensions (L × W) from 160 μm × 100 μm down to 9 μm × 3 μm on the obtained Si/CaF2 surfaces.

CaF2 layers were grown on moderately doped (ND = 1015 cm−3) and highly doped (ND = 5 × 1018 cm−3) n-Si(111) substrates with a miscut angle of 5 to 10 minutes. Following careful chemical treatment of Si(111) surface, a protective oxide layer was formed using the method of Shiraki45 and subsequently removed by annealing for 2 minutes at 1200 oC under ultra-high vacuum conditions ( ~ 10−8 − 10−7 Pa). After this, the CaF2 film with 2 nm thickness was grown on the obtained atomically clean 7 × 7 Si(111) surface using an MBE process with the optimal growth temperature of 250oC and deposition rate of about 1.3 nm min−1. A crystalline quality of the obtained CaF2 layers was examined in situ using reflection high-energy electron diffraction (RHEED)46 with an electron energy of 15 keV. The corresponding RHEED patterns which confirm high crystallinity with single-crystal structure of our thin CaF2 films can be found in the Supporting Information of our previous work22.

Our GFETs were fabricated on the obtained epitaxial Si/CaF2 substrates using conventional photolithography. After defining the source and drain contact regions by photolithography, 10 nm Al2O3 was deposited by plasma enhanced atomic layer deposition to isolate the contact pads and source and drain metals were deposited by sputtering 25 nm Pd, followed by a lift-off process. After fabricating the contacts, commercially available chemical vapor deposited graphene was transferred on the substrate by a PMMA assisted method. Finally, the graphene was patterned by oxygen plasma to form the transistor channel which is bottom-contacted by Pd metal.

Using a similar approach, we have also fabricated back-gated GFETs with 90 nm SiO2 and 36 nm Al2O3 insulators to be used for reference in hysteresis comparison. However, considering larger insulator thickness, no isolation of contact pads was needed in that case.

Device characterization

Electrical characterization of our GFETs with CaF2 consisted in the measurements of the ID − VG characteristics and hysteresis dynamics. These measurements were performed using a Keithley 2636 parameter analyzer in the chamber of a Lakeshore probestation in a vacuum ( ~ 5 × 10−6 torr), in complete darkness and at temperatures ranging from 25 to 175 oC, with the days-long measurements at 175oC being also considered as an annealing step. The hysteresis of the ID − VG characteristics was studied using our established measurement technique36 based on double sweeps with varied sweep times. The hysteresis width was obtained as a difference of VDirac between forward and reverse sweep ID − VG characteristics. We express our results by plotting the hysteresis widths ΔVH versus the reciprocal sweep time 1/tsw. For comparing hysteresis widths and Dirac point shifts for different devices and measurement conditions, we extract ΔVH for a sweep time in the kilosecond range, normalize it by EOT and plot it versus the effective gate field \(({V}_{{{{\rm{G,max}}}}}-{V}_{{{{\rm{G,min}}}}})/{d}_{{{{\rm{ins}}}}}\), where \(({V}_{{{{\rm{G,max}}}}}-{V}_{{{{\rm{G,min}}}}})\) is the width of the sweep range and dins is the insulator thickness, and also versus EOT.

Data availability

The data that support the findings of this work are available from the corresponding author upon reasonable request.

References

Novoselov, K. et al. Electric field effect in atomically thin carbon films. Science 306, 666–669 (2004).

Geim, A. & Novoselov, K. The rise of graphene. Nat. Mater. 6, 183–191 (2007).

Geng, H. et al. Graphene van der Waals heterostructures for high-performance photodetectors. J. Mater. Chem. C 7, 11056–11067 (2019).

Béraud, A. et al. Graphene field-effect transistors as bioanalytical sensors: Design, operation and performance. Analyst 146, 403–428 (2021).

Liao, L. & Duan, X. Graphene for radio frequency electronics. Mater. Today 15, 328–338 (2012).

Lemme, M., Echtermeyer, T., Baus, M. & Kurz, H. A graphene field effect device. IEEE Electron Device Lett. 27, 1–12 (2007).

Fleetwood, D. “Border Traps” in MOS devices. IEEE Trans. Nucl. Sci. 39, 269–271 (1992).

Wang, H., Wu, Y., Cong, C., Shang, J. & Yu, T. Hysteresis of electronic transport in graphene transistors. ACS Nano 4, 7221–7228 (2010).

He, G. et al. Thermally assisted nonvolatile memory in monolayer MoS2 transistors. Nano Lett. 16, 6445–6451 (2016).

Illarionov, Y. et al. Insulators for 2D nanoelectronics: The gap to bridge. Nat. Commun. 3385 (2020).

Gannett, W. et al. Boron nitride substrates for high mobility chemical vapor deposited graphene. Appl. Phys. Lett. 98, 242105 (2011).

Petrone, N. et al. Chemical vapor deposition-derived graphene with electrical performance of exfoliated graphene. Nano Lett. 12, 2751–2756 (2012).

De Fazio, D. et al. High-mobility, wet-transferred graphene grown by chemical vapor deposition. ACS Nano 13, 8926–8935 (2019).

Hui, F. et al. Synthesis of large-area multilayer hexagonal boron nitride sheets on iron substrates and its use in resistive switching devices. 2D Mater. 5, 031011 (2018).

Lemme, M., Akinwande, D., Huyghebaert, C. & Stampfer, C. 2D materials for future heterogeneous electronics. Nat. Commun. 13, 1392 (2022).

Hartnett, J., Fowler, A., Tobar, M. & Krupka, J. The microwave characterization of single crystal lithium and calcium fluoride at cryogenic temperatures. IEEE Trans. Ultrason. Ferroelectr. Freq. 51, 380–386 (2004).

Hayes, W. Crystals with the fluorite structure (Clarendon Press, 1974).

Koma, A., Saiki, K. & Sato, Y. Heteroepitaxy of a two-dimensional material on a three-dimensional material. Appl. Surf. Sci. 41, 451–456 (1990).

Illarionov, Y., Vexler, M., Fedorov, V., Suturin, S. & Sokolov, N. Electrical and optical characterization of Au/CaF2/p-Si(111) tunnel-injection diodes. J. Appl. Phys. 115, 223706 (2014).

Vishwanath, S. et al. Comprehensive structural and optical characterization of MBE grown MoSe2 on graphite, CaF2 and graphene. 2D Mater. 2, 024007 (2015).

Vishwanath, S. et al. MBE growth of few-layer 2H-MoTe2 on 3D substrates. J. Cryst. Growth 482, 61–69 (2018).

Illarionov, Y. et al. Ultrathin calcium fluoride insulators for two-dimensional field-effect transistors. Nat. Electron. 2, 230–235 (2019).

Illarionov, Y. et al. Crystalline calcium fluoride: A record-thin insulator for nanoscale 2D electronics. In IEEE Device Research Conference (DRC), 1–2 (2020).

Nazzari, D. et al. Epitaxial growth of crystalline CaF2 on silicene. ACS Appl. Mater. Interfaces 14, 32675–32682 (2022).

Ravez, J. The inorganie fluoride and oxyfluoride ferroelectrics. J. Phys. III 7, 1129–1144 (1997).

Kaveev, A. et al. Epitaxial growth on silicon and characterization of MnF2 and ZnF2 layers with metastable orthorhombic structure. J. Appl. Phys. 98, 013519 (2005).

Banshchikov, A. et al. Epitaxial layers of nickel fluoride on Si (111): Growth and stabilization of the orthorhombic phase. Phys. Solid State 57, 1647–1652 (2015).

Wen, C. et al. Dielectric properties of ultrathin CaF2 ionic crystals. Adv. Mater. 32, 2002525 (2020).

Peters, A., Turvey, S. & Horsfall, A. High temperature graphene sensors for harsh environment current sensing. In IEEE SENSORS, 1–4 (2019).

Asselberghs, I. et al. Wafer-scale integration of double gated WS2 transistors in 300mm Si CMOS FAB. In IEEE International Electron Devices Meeting (IEDM), 40–2 (2020).

Tilmann, R. et al. Identification of ubiquitously present polymeric adlayers on 2D transition metal dichalcogenides. ACS Nano 17, 10617–10627 (2023).

Robertson, J. High dielectric constant oxides. European Phys. J. Appl. Phys. 28, 265–291 (2004).

Illarionov, Y. et al. Bias-temperature instability in single-layer graphene field-effect transistors. Appl. Phys. Lett. 105, 143507 (2014).

Asenov, A., Balasubramaniam, R., Brown, A. R. & Davies, H. RTS amplitudes in decananometer MOSFETs: 3-D simulation study. IEEE Trans. Electron Devices 50, 839–845 (2003).

Knobloch, T. et al. Improving stability in two-dimensional transistors with amorphous gate oxides by fermi-level tuning. Nat. Electron. 5, 356–366 (2022).

Illarionov, Y. et al. The role of charge trapping in MoS2/SiO2 and MoS2/hBN field-effect transistors. 2D Mater. 3, 035004 (2016).

Grasser, T. et al. The paradigm shift in understanding the bias temperature instability: From reaction-diffusion to switching oxide traps. IEEE Trans. Electron Devices 58, 3652–3666 (2011).

Waldhoer, D. et al. Silicon-impurity defects in calcium fluoride: A first principles study. In ESSDERC 2022-IEEE 52nd European Solid-State Device Research Conference (ESSDERC), 380–383 (IEEE, 2022).

Illarionov, Y. et al. Long-term stability and reliability of black phosphorus field-effect transistors. ACS Nano 10, 9543–9549 (2016).

Illarionov, Y. et al. Energetic mapping of oxide traps in MoS2 field-effect transistors. 2D Mater. 4, 025108 (2017).

Illarionov, Y. et al. Improved hysteresis and reliability of MoS2 transistors with high-quality CVD growth and Al2O3 encapsulation. IEEE Electron Device Lett. 38, 1763–1766 (2017).

Rzepa, G. et al. Comphy—a compact-physics framework for unified modeling of BTI. Microelectron. Reliab. 85, 49–65 (2018).

IRDS More Moore (IEEE Tech. Rep., 2022).

Kumar, P. et al. Hybrid architecture based on two-dimensional memristor crossbar array and CMOS integrated circuit for edge computing. npj 2D Mater. Appl. 6, 1–10 (2022).

Ishizaka, A. & Shiraki, Y. Low temperature surface cleaning of silicon and its application to silicon MBE. J. Electrochem. Soc. 133, 666–671 (1986).

Sokolov, N., Alvarez, J. & Yakovlev, N. Fluoride layers and superlattices grown by MBE on Si(111): Dynamic RHEED and Sm2+ photoluminescence studies. Appl. Surf. Sci. 60, 421–425 (1992).

Acknowledgements

This research was funded in part by the Austrian Science Fund (FWF) [10.55776/I5296]. For open access purposes, the author has applied a CC BY public copyright license to any author accepted manuscript version arising from this submission. A.G.B., I.A.I., N.S.S. are grateful for the support within RFBR grant 21-52-14007. M.I.V. acknowledges financial support by the Ministry of Science and Higher Education of the Russian Federation under project no. 075-15-2020-790. Furthermore, T.K. acknowledges financial support through the FFG under project no. 1755510 and also Austrian Science Fund (FWF) [I2606-N30, I4123-N30 (joint project with DFG LE 2440/8-1)]. M.C.L. acknowledges financial support through the German Federal Ministry of Education and Research grant GIMMIK (03XP0210) and DFG grants MOSTFLEX (LE 2440/7-1) and ULTIMOS2 (LE 2440/8-1). Z.W. acknowledges financial support through the DFG grant MOSTFLEX (WA 4139/3-1). D.N. acknowledges financial support through the DFG grant GLECSII (NE1633/3-2). Additionally, B.U., Z.W., D.N. and M.C.L. acknowledge funding from the European Union’s Horizon 2020 research and innovation programme under grant agreements 2D-EPL (952792), GrapheneCore3 (881603) and WiPLASH (863337). M.W. acknowledges financial support by the Austrian Federal Ministry for Digital and Economic Affairs; the National Foundation for Research, Technology and Development; and the Christian Doppler Research Association. Y.Y.I. is grateful for the financial support by Shenzhen Science and Technology Program 20231115150611001 and the start up fund provided by SUSTech. Useful discussions of growth experiment results with Dr. S.M. Suturin are greatly appreciated.

Author information

Authors and Affiliations

Contributions

Y.Y.I. performed the measurements of device-to-device variability, hysteresis and BTI and wrote the manuscript. T.K. contributed to data analysis, creating Fig. 8 and the corresponding discussion in the text. B.U. fabricated GFETs. A.G.B. and I.A.I. carried out growth of CaF2. M.W. and B.M. contributed to editing the text. M.O. and S.L.S. conducted Raman, SEM and AFM analysis. V.S., M.I.V., D.N., Z.W., M.C.L, N.S.S. and T.G. supervised the research. All authors discussed the results and contributed to the preparation of the manuscript.

Corresponding authors

Ethics declarations

Competing interests

The authors declare no competing interests.

Additional information

Publisher’s note Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Supplementary information

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons licence, and indicate if changes were made. The images or other third party material in this article are included in the article’s Creative Commons licence, unless indicated otherwise in a credit line to the material. If material is not included in the article’s Creative Commons licence and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this licence, visit http://creativecommons.org/licenses/by/4.0/.

About this article

Cite this article

Illarionov, Y.Y., Knobloch, T., Uzlu, B. et al. Variability and high temperature reliability of graphene field-effect transistors with thin epitaxial CaF2 insulators. npj 2D Mater Appl 8, 23 (2024). https://doi.org/10.1038/s41699-024-00461-0

Received:

Accepted:

Published:

DOI: https://doi.org/10.1038/s41699-024-00461-0